- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- QSPI dual flash - addressing

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

QSPI dual flash - addressing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-11 9:26 AM

I'm porting a QSPI bootloader over from a design that 1 flash chip to 2 flash chips in parallel (10 bit mode, common CS). I am not sure how the addressing works now that there are 2 chips in parallel. I feel like the only thing STM32 says on the matter is in AN4760 in that even bytes goto one flash 1 and odd bytes goto the flash 2.

If I have something that is addressed at 0x1000 internally by the STM32, when sending QSPI commands to write or erase to the QSPI do I need to double the address (to 0x2000) first? Or does the QSPI interface in the STM32 already do that for me?

Solved! Go to Solution.

- Labels:

-

QSPI

-

STM32H7 series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-11 9:39 AM

The implementation is a bit clumsy and confusing.

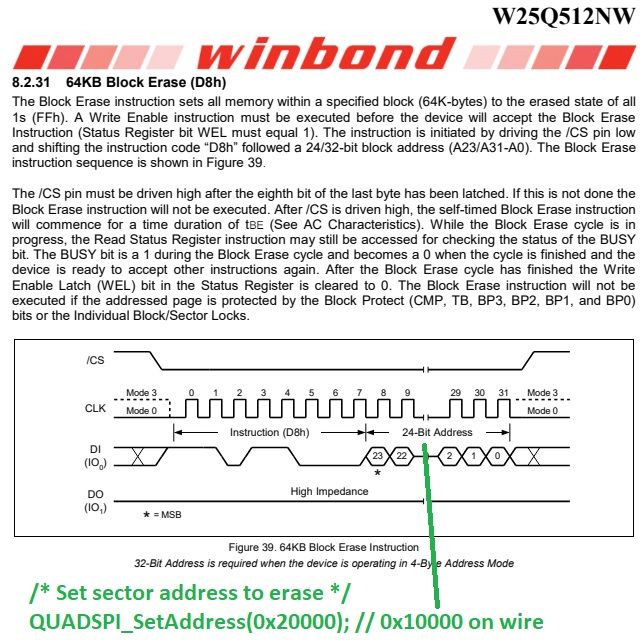

In "DUAL" mode both devices need to be the same, content is multiplexed at a BYTE level. So all send and receive commands are sent to both devices and the data sent and received alternates between them.

The command and address goes to both devices in parallel. The address is divided by TWO

Pages that were 0x100 or 0x1000 will now be 0x200 or 0x2000, see also addresses for erase, etc.

The status comes back in pairs, and devices might not be synchronized, ie one might complete the erase before the other, you need to wait for BOTH to complete fully.

To erase the second 64KB block in both devices (0x10000 on a single device), you pass the 0x20000 address, and it will erase 128KB across both devices.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-11 9:39 AM

The implementation is a bit clumsy and confusing.

In "DUAL" mode both devices need to be the same, content is multiplexed at a BYTE level. So all send and receive commands are sent to both devices and the data sent and received alternates between them.

The command and address goes to both devices in parallel. The address is divided by TWO

Pages that were 0x100 or 0x1000 will now be 0x200 or 0x2000, see also addresses for erase, etc.

The status comes back in pairs, and devices might not be synchronized, ie one might complete the erase before the other, you need to wait for BOTH to complete fully.

To erase the second 64KB block in both devices (0x10000 on a single device), you pass the 0x20000 address, and it will erase 128KB across both devices.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-11 9:53 AM

Thanks for the excellent writeup.

So if something is at address at 0x1000 on the STM32, I should pass 0x500 to the QSPI command?

For addressing, do I have to do that division manually or does the QSPI interface already do that for me if I'm in dual port mode?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-11 10:02 AM - edited 2023-08-11 10:18 AM

The QSPI peripheral does the address division, so the address you pass as a parameter is divided by 2 on the wire, A0 would then select one device or the other, although I wouldn't rely on that. Do everything with the expectation that both devices are involved.

As per my example you set Address = 0x20000, the devices see 0x10000 on the wire.

BTW 0x1000 / 2 = 0x800

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-11 10:14 AM

Write Page (0x02) which was 256-bytes is now effectively 512-bytes at 512-byte boundaries, ie 0x0000,0x0200,0x0400,..

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-28 5:08 AM

hello, I need to change the qspi flash from single to dual mode...Does it make any difference in the loader? Can I use my previous loader for programming both flashes? (no changes in flash1 pins)

thank you in advance for your answer

- LSM6DSO I3C SETDASA in STM32 MCUs Embedded software

- ST-LINKV3 over VirtualHere (USB over IP) in STM32 MCUs Products

- External QSPI NOR flash read and write operation in STM32 MCUs Embedded software

- digital MEMS MIC (MP34DT05) issue on STMH747I-DISCO in STM32 MCUs Embedded software

- Case STM32H7 – External Flash (XIP via OctoSPI) and Large External RAM (~256MB) Interfacing Feasibility in STM32 MCUs Products