- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Multiplexed OCTOSPI in STM32H7B0RBT6

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Multiplexed OCTOSPI in STM32H7B0RBT6

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 10:31 AM

Hi,

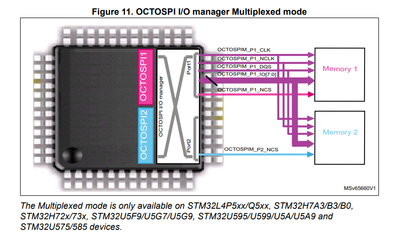

I would like to know if it is possible to have the mutiplexed octospi in the microcontroller stm32h7b0rt6 as it mentionned in AN5050 in Figure 11

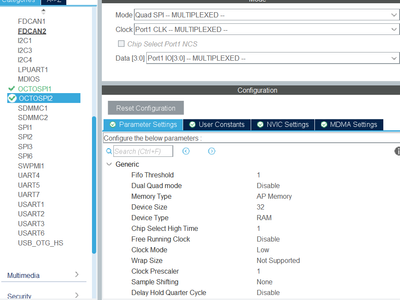

cause when I tried to configure it using the CubeMx the CS pin for OCTOSPI2 is not found as it is mandatory to have such pin for the multiplexing mode managed by the internal hardware arbiter :

Do we have a such feature in our microcontroller STM32H7b0rbt6 ??

Solved! Go to Solution.

- Labels:

-

STM32H7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 12:41 PM - edited 2023-09-13 12:42 PM

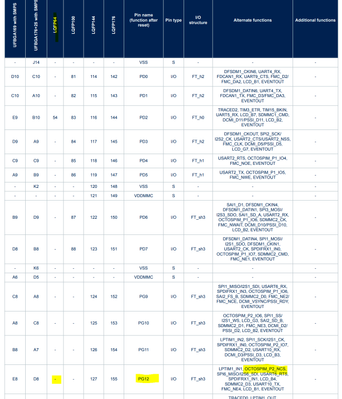

Port 2 CS pin is PG12, which doesn't exist on the LQFP64 or LQFP100 version of that chip.

So effectively, you cannot use that feature on that chip, although it's supported on larger packages within that family.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 10:50 AM - edited 2023-09-13 01:00 PM

Hello @ALAMI_Othmane

As you can see her:

The multiplexed octospi configuration is possible with your STM32H7B0.

But tacking a look at the datasheet of the STM32H7B0RBT6 we find out tha the OCTOSPIM_P2_NCS doesn't exist so is impossible to use the mutiplexed octospi configuration in the STM32H7B0RBT6

Best regards.

II

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 12:41 PM - edited 2023-09-13 12:42 PM

Port 2 CS pin is PG12, which doesn't exist on the LQFP64 or LQFP100 version of that chip.

So effectively, you cannot use that feature on that chip, although it's supported on larger packages within that family.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 01:57 PM

What is the end goal? Which QUAD/OCTO SPI parts are you using, off of which pins?

The OCTOSPIM should be able to selectively map high/low pin blocks, and control pins. There may be other ways/tricks to getting specific combinations of devices working

Up vote any posts that you find helpful, it shows what's working..