- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- How to configure STM32H743 to reach maximum ADC sa...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to configure STM32H743 to reach maximum ADC sampling frequency? (3.6 MSPS or 3.6 MHz

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-12 10:39 PM

Hi. I am just learning to use STM, this board was bought to me by my employer. Please, look at my clock config and code, and tell me, what is wrong.

ADC clock is set to 36MHZ, ADC prescaler = 1, sampling time is set to 1.5 cycles, conversion time is 8.5 cycles according to datasheet. In theory, ADC sampling freq must be 36/(1.5 + 8.5) = 3.6 MHz. ADC is configured with continious conversion mode and interrupt by EOC.

I counted number of interrupts per second, and send this value by UART. It is not 3.6MHZ, as expected, but 1.8 MHz! Absolutely cant't understand, what is wrong.

void ADC_IRQHandler(void)

{

*((uint16_t*)(data+2*adc_values_count)) = hadc1.Instance->DR;

++adc_values_count;

if (adc_values_count==PACKET_VALUES_COUNT)

{

hadc1.Instance->IER &= ~ADC_IT_EOC;

//netconn_send(udp_conn, buf);

adc_values_count = 0;

++adc_packets_count;

hadc1.Instance->IER |= ADC_IT_EOC;

}

}

static void ADC1_Init(void)

{

ADC_MultiModeTypeDef multimode = {0};

ADC_ChannelConfTypeDef sConfig = {0};

hadc1.Instance = ADC1;

hadc1.Init.ClockPrescaler = ADC_CLOCK_ASYNC_DIV1;

hadc1.Init.Resolution = ADC_RESOLUTION_16B;

hadc1.Init.ScanConvMode = ADC_SCAN_DISABLE;

hadc1.Init.EOCSelection = ADC_EOC_SINGLE_CONV;

hadc1.Init.LowPowerAutoWait = DISABLE;

hadc1.Init.ContinuousConvMode = ENABLE;

hadc1.Init.NbrOfConversion = 1;

hadc1.Init.DiscontinuousConvMode = DISABLE;

hadc1.Init.ExternalTrigConv = ADC_SOFTWARE_START;

hadc1.Init.ExternalTrigConvEdge = ADC_EXTERNALTRIGCONVEDGE_NONE;

hadc1.Init.ConversionDataManagement = ADC_CONVERSIONDATA_DR;

//hadc1.Init.Overrun = ADC_OVR_DATA_PRESERVED;

hadc1.Init.Overrun = ADC_OVR_DATA_OVERWRITTEN;

hadc1.Init.LeftBitShift = ADC_LEFTBITSHIFT_NONE;

hadc1.Init.OversamplingMode = DISABLE;

if (HAL_ADC_Init(&hadc1) != HAL_OK)

{

Error_Handler();

}

multimode.Mode = ADC_MODE_INDEPENDENT;

if (HAL_ADCEx_MultiModeConfigChannel(&hadc1, &multimode) != HAL_OK)

{

Error_Handler();

}

sConfig.Channel = ADC_CHANNEL_5;

sConfig.Rank = ADC_REGULAR_RANK_1;

sConfig.SamplingTime = ADC_SAMPLETIME_1CYCLE_5;

//sConfig.SamplingTime = ADC_SAMPLETIME_810CYCLES_5;

sConfig.SingleDiff = ADC_SINGLE_ENDED;

sConfig.OffsetNumber = ADC_OFFSET_NONE;

sConfig.Offset = 0;

if (HAL_ADC_ConfigChannel(&hadc1, &sConfig) != HAL_OK)

{

Error_Handler();

}

if (HAL_ADCEx_Calibration_Start(&hadc1, ADC_CALIB_OFFSET_LINEARITY, ADC_SINGLE_ENDED) != HAL_OK)

{

/* Calibration Error */

Error_Handler();

}

void SystemClock_Config(void)

{

RCC_OscInitTypeDef RCC_OscInitStruct = {0};

RCC_ClkInitTypeDef RCC_ClkInitStruct = {0};

RCC_PeriphCLKInitTypeDef PeriphClkInitStruct = {0};

/*!< Supply configuration update enable */

HAL_PWREx_ConfigSupply(PWR_LDO_SUPPLY);

__HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE0);

while(!__HAL_PWR_GET_FLAG(PWR_FLAG_VOSRDY))

{

}

/* Enable D2 domain SRAM3 Clock (0x30040000 AXI)*/

__HAL_RCC_D2SRAM3_CLK_ENABLE();

//HSI can be off when ADC is on HSE

//RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSI|RCC_OSCILLATORTYPE_HSE;

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSE;

RCC_OscInitStruct.HSEState = RCC_HSE_ON;

RCC_OscInitStruct.HSEState = RCC_HSE_BYPASS;

//RCC_OscInitStruct.HSIState = RCC_HSI_DIV2;

//RCC_OscInitStruct.HSICalibrationValue = RCC_HSICALIBRATION_DEFAULT;

RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON;

RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE;

RCC_OscInitStruct.PLL.PLLM = 4;

RCC_OscInitStruct.PLL.PLLN = 400;

RCC_OscInitStruct.PLL.PLLP = 2;

RCC_OscInitStruct.PLL.PLLQ = 2;

RCC_OscInitStruct.PLL.PLLR = 2;

RCC_OscInitStruct.PLL.PLLRGE = RCC_PLL1VCIRANGE_1;

RCC_OscInitStruct.PLL.PLLVCOSEL = RCC_PLL1VCOWIDE;

RCC_OscInitStruct.PLL.PLLFRACN = 0;

if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK)

{

Error_Handler();

}

/** Initializes the CPU, AHB and APB busses clocks

*/

RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_HCLK|RCC_CLOCKTYPE_SYSCLK

|RCC_CLOCKTYPE_PCLK1|RCC_CLOCKTYPE_PCLK2

|RCC_CLOCKTYPE_D3PCLK1|RCC_CLOCKTYPE_D1PCLK1;

RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK;

RCC_ClkInitStruct.SYSCLKDivider = RCC_SYSCLK_DIV1;

RCC_ClkInitStruct.AHBCLKDivider = RCC_HCLK_DIV2;

RCC_ClkInitStruct.APB3CLKDivider = RCC_APB3_DIV2;

RCC_ClkInitStruct.APB1CLKDivider = RCC_APB1_DIV2;

RCC_ClkInitStruct.APB2CLKDivider = RCC_APB2_DIV2;

RCC_ClkInitStruct.APB4CLKDivider = RCC_APB4_DIV2;

if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_2) != HAL_OK)

{

Error_Handler();

}

PeriphClkInitStruct.PeriphClockSelection = RCC_PERIPHCLK_UART7|RCC_PERIPHCLK_ADC;

PeriphClkInitStruct.PLL2.PLL2M = 4;

PeriphClkInitStruct.PLL2.PLL2N = 450;

PeriphClkInitStruct.PLL2.PLL2P = 25;

PeriphClkInitStruct.PLL2.PLL2Q = 2;

PeriphClkInitStruct.PLL2.PLL2R = 2;

PeriphClkInitStruct.PLL2.PLL2RGE = RCC_PLL2VCIRANGE_1;

PeriphClkInitStruct.PLL2.PLL2VCOSEL = RCC_PLL2VCOWIDE;

//PeriphClkInitStruct.PLL2.PLL2VCOSEL = RCC_PLL2VCOMEDIUM;

PeriphClkInitStruct.PLL2.PLL2FRACN = 0;

PeriphClkInitStruct.Usart234578ClockSelection = RCC_USART234578CLKSOURCE_D2PCLK1;

PeriphClkInitStruct.AdcClockSelection = RCC_ADCCLKSOURCE_PLL2;

if (HAL_RCCEx_PeriphCLKConfig(&PeriphClkInitStruct) != HAL_OK)

{

Error_Handler();

}

}- Labels:

-

ADC

-

STM32H7 series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-08-05 9:58 PM

Have you found the answer yet? I also experiences same thing.

I tested both synchronous and asynchronous clock on my custom STM32H750VB.

All produce same result which is half of calculated value.

I even lower the ADC Clock to match what stated in datasheet(Max 19Mhz).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-08-12 1:22 AM

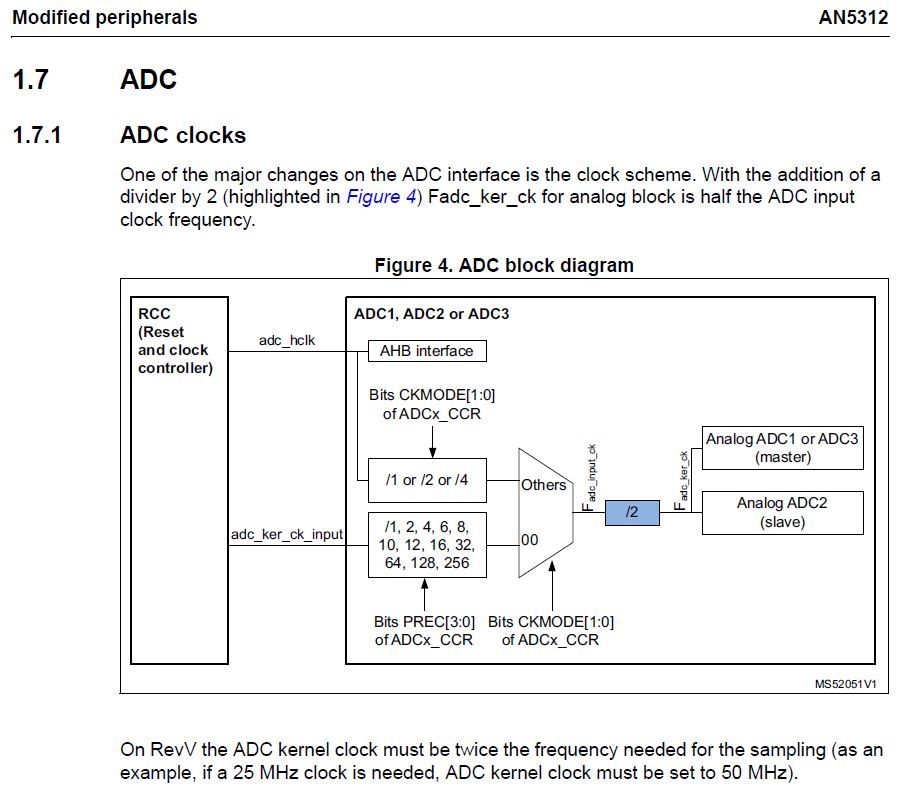

I found the answer, the STM32 Rev V had additional divider by 2,

Hence in order to get 19Mhz, the ADCCLK need to be 38Mhz.

Hope this help for other.

- HAL_TIM_IC_ReadChannelCapturedValue returns 0 in STM32 MCUs Embedded software

- Clock configuration in STM32CubeMX2 (MCUs)

- Tracing on STM32H743 in Others: STM32 MCUs related

- Request for Guidance on LoRa-E5 (STM32WLE5JC) LoRa TX/RX Setup in STM32CubeIDE 2.1.0 in STM32 MCUs Wireless

- LTDC Configuration for DE-Only RGB Display (No HSYNC / VSYNC) on STM32H743 – Display Not Working in STM32 MCUs Products