- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- How DMA works in UART

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How DMA works in UART

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-18 01:46 PM

Hello !

I've been wondering how DMA works in UART.

I've checked some codes for example HAL_UART_Transmit_DMA(). I know it is set to sned 8 bit to peripheral. But I wondered when DMA knows that UART sent 8 bit when it is TX DMA or recevied 8 bit when it is in RX DMA. In this case it is TX.

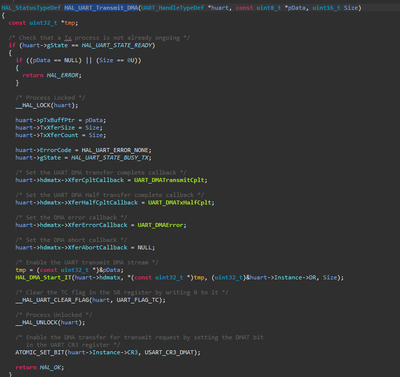

I've checked what HAL_UART_Transmit_DMA() does :

And there was this HAL_DMA_Start_IT(). So it works that DMA sends it's data from memory to UART TX registers. Ok. So tmp is the memory we have the data, and the Instance-> DR is the register the data must be sent.

So where exactly there is info about turning on the UART to transmit data, and when does the DMA know that UART sent 8 bit and is ready to send another 8 bits ?

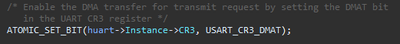

I've also noticed this :

But I don't understand what it does ? It turn on the UART transmit ?

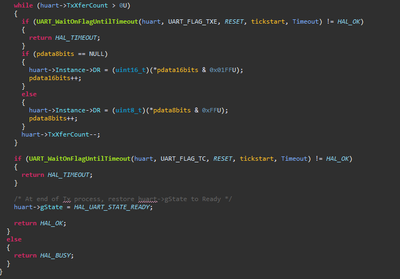

Sorry for being to picky I was quite a bit confused due to the fact that in HAL_UART_Transmit there is a while which has a counter that sends 1 byte

Although I don't know if it has any info back whether it has sent the data or not. It's so confusing ... There is no waiting time or anything.

Solved! Go to Solution.

- Labels:

-

STM32L0 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-19 01:30 PM

On the picture, note the thin arrow labeled DMA request. This is signal from a peripheral to DMA that tells the DMA to move next piece of data. UART has two these request lines, for RX and TX. Every DMA-capable peripheral has these lines. All other information (addresses of UART registers, direction of move...) you specify in the DMA channel configuration.

> How he searches the devices/memory

Don't work (or study) too hard. Drink water, take a good nap. Then you'll understand.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-19 01:50 PM

> Don't work (or study) too hard. Drink water, take a good nap. Then you'll understand.

Perhaps you are right, but it's hard to find infomation about it like with UART. Usually pictures shows only data bus and RX, TX pin, but in STM or other devices there are some registers, so I tried to undestand them trying to imagine how it works in logic gates level, but it's hard and I didn't know where to find source to learn. I found out people know these stuff like it's a basic so I tried to attempt on understanding it as well, or rather tried to understand how it works in code and in hardware as well ;> Maybe it is useless dunno, just saw that people know it so I understood it might be a good idea to learn it for FPGA purposes as well.

>On the picture, note the thin arrow labeled DMA request. This is signal from a peripheral to DMA that tells the DMA to move next piece of data. UART has two these request lines, for RX and TX. Every DMA-capable peripheral has these lines. All other information (addresses of UART registers, direction of move...) you specify in the DMA channel configuration.

So CPU configurates the DMA for which request he has to wait, addresses ect. the UART only turns on the DMA request transmission.

I have so many questions but maybe it is not suitible here. I will also wait for the answer from JW, most parts I guess I understood.

Learning basics can be hard but learning how code works in the beggining is also hard ;D

Thanks Pavel.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-19 02:12 PM

The RM does not go to gate-level details. It's expected that you have prior knowledge of general working of basic mcu constituents such as UART and DMA, from school/courses/books or any other general electronics-related form of education. The RM then fills in the STM32-specific details.

So, I'm going to answer some of your concrete questions; but you should start seeking a more thorough introductory material, as you are not going to get a full tutorial here, we just don't have time and space for that.

---

> Something like this ?

That's a parallel-loaded shift register (sometimes also denoted as parallel-in-serial-out, or PISO); yes, that's one part of it. The other is the bit counter I've mentioned together with shift register. And of course there's a bunch of auxiliary glue logic to gate clocks, determine counter being at zero, etc.

> UART devices pictures shows only data bus and TX RX like here :

Yes. That's the same as when you talk about a building, say the Empire State Building in New York - the vast majority of public information is how it looks like from the outside; only a few people are interested in, and have seen, the blueprints according which it has been built.

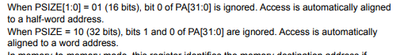

> Like bits 1 and 0 of PA[31:0] are ignored ?

Yes, the zeroth and first bit are used as if they were zero. It means, the address is rounded down to the nearest multiple of four.

> The picture how DMA works doesn't tell a lot :

That's because again, you are looking at a block schematics of all elevators in the Empire State Building, together with the related electric power grid and the traffic distribution. You want to know how one elevator (here: channel) works, so read the description of channel-related registers at the end of the DMA chapter, and then read the functional description. It takes several re-reads, and I recommend you to try to draw yourself block schematics and charts, according to what you are reading.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-19 02:45 PM

> So, I'm going to answer some of your concrete questions; but you should start seeking a more thorough introductory material, as you are not going to get a full tutorial here, we just don't have time and space for that.

Understandable, where can I find these materials, recommendations ?

>Yes. That's the same as when you talk about a building, say the Empire State Building in New York - the vast majority of public information is how it looks like from the outside; only a few people are interested in, and have seen, the blueprints according which it has been built.

I thought that when everybody know how UART is working from logic gates then I thought it might be helpful in understanding stuffs or how to write charts etc. So I wanted to know where I can start.

>Yes, the zeroth and first bit are used as if they were zero. It means, the address is rounded down to the nearest multiple of four.

I still don't understand it, what I understood from this :

Is that all 32 bits in PA is ignored because it consist of 0 and 1. Because it says it ignores 1 and 0 in PA[31:0].

That's what I understood because it says it ignores these values in PA

>That's because again, you are looking at a block schematics of all elevators in the Empire State Building, together with the related electric power grid and the traffic distribution. You want to know how one elevator (here: channel) works, so read the description of channel-related registers at the end of the DMA chapter, and then read the functional description. It takes several re-reads, and I recommend you to try to draw yourself block schematics and charts, according to what you are reading.

I don't know how to start with it. I don't know what to achieve from DMA so hence I don't know what to start with ;D

So I should ignore how to works in logic gate way ? I thought it might be helpfull in understanding why I need to set some bits in DMA or in UART or what should be done in code and what is done in hardware without code.

So I don't know how to start learning it, from logic gate side or from just the code but not everything is in code etc.

> It's expected that you have prior knowledge of general working of basic mcu constituents such as UART and DMA, from school/courses/books or any other general electronics-related form of education.

I was only taught how simple things work like Adder, Half-Adder, simple multiplexer, basic operations like OR, AND, Moore machine. But the data bus or how memory works is new thing to me and I tried to learn on my own. Or how UART works in logic thing or DMA or more devices is new, or how 8 wires can send and receive data from memory, new things ;>

Thanks JW !

- « Previous

-

- 1

- 2

- Next »

- stm32f469i CAN Not Working in STM32 MCUs Products

- STM32CubeIDE only running code from one project in STM32 MCUs Products

- STM32MP157f-DK2 - Problem with flashing in STM32CubeProgrammer (MCUs)

- Question related to post "How to create a project for STM32H7 with Ethernet and LwIP stack working" in STM32 MCUs Embedded software

- STM32G030C8Tx can not communicate with BTT TMC2209 in STM32 MCUs Motor control