- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Generate 2 second break from UART

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Generate 2 second break from UART

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-11-15 11:12 PM

I'm trying to generate a 2 second break from USART1 on a STM32F105. It's needed for a custom protocol running on top of LIN: the TX line must be driven low for 2 seconds.

UARTs like 8250 and 16550 have a Set Break Enable Bit (SBE) in their Line Control Register that stays set until it's cleared by software, but the STM32F1 UART appears to reset the bit in hardware.

Section 27.3.1 of the STM32F1 reference manual says:

"A Break character is interpreted on receiving “0�?s for a frame period. At the end of the break frame the transmitter inserts either 1 or 2 stop bits (logic “1�? bit) to acknowledge the start bit."

Further down in 27.3.2 Break Characters it says

"Setting the SBK bit transmits a break character. The break frame length depends on the M bit (see Figure 279).

If the SBK bit is set to ‘1’ a break character is sent on the TX line after completing the current character transmission. This bit is reset by hardware when the break character is completed (during the stop bit of the break character). The USART inserts a logic 1 bit at the end of the last break frame to guarantee the recognition of the start bit of the next frame."

"If the software resets the SBK bit before the commencement of break transmission, the break character will not be transmitted. For two consecutive breaks, the SBK bit should be set after the stop bit of the previous break."

I interpret that as that the break can only be M bits long (which is 8 for me ), then a stop bit is inserted.

Can I generate longer breaks?

As a naive experiment I tried continuously sending break upon a completed transmission.

void USART1_IRQHandler(void) {

if (Port->SR & USART_SR_TXE) {

// Enable interrupt on completed transmission

Port->CR1 |= USART_CR1_TCIE;

// Generate a break signal

Port->CR1 |= USART_CR1_SBK;

}

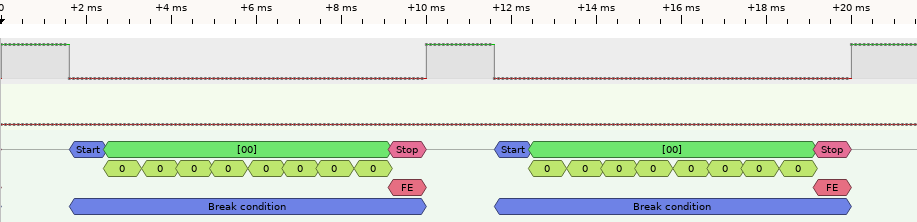

}This gave me this output in my logic analyzer (the uart is running at 1200 baud): In between the breaks, there some time where the line goes idle (or are those stop bits generated by the break itself?).

Any suggestions on how to drive the TX line low for more than one character (M) width?

- Can I modify the uart configuration somehow?

- Code the ISR in a different way?

- Temporily switch the pins to outputs? But then what is the time needed for the uart to stabilize when I re-enable it?

Solved! Go to Solution.

- Labels:

-

STM32F1 Series

-

UART-USART

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-11-15 11:18 PM

I understand your task, but customarily, on RS232, *any* MARK longer than start+data(+parity) bits is considered BREAK, so ST's approach is legitimate. In other words, it's your application which requires a non-standard BREAK, so you need to generate it "manually", by setting the pin to output.

> But then what is the time needed for the uart to stabilize when I re-enable it?

You'll switch only the Tx, so none.

More precisely, you need no time to *stabilize* UART, but you'd need some time (probably one bit's time) between the break trailing end and the first startbit for the UART on the other end to be able to distinguish them.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-11-15 11:18 PM

I understand your task, but customarily, on RS232, *any* MARK longer than start+data(+parity) bits is considered BREAK, so ST's approach is legitimate. In other words, it's your application which requires a non-standard BREAK, so you need to generate it "manually", by setting the pin to output.

> But then what is the time needed for the uart to stabilize when I re-enable it?

You'll switch only the Tx, so none.

More precisely, you need no time to *stabilize* UART, but you'd need some time (probably one bit's time) between the break trailing end and the first startbit for the UART on the other end to be able to distinguish them.

JW

- VSCode Extension v3.9.0 Breaks Debugger in STM32CubeIDE for Visual Studio Code (MCUs)

- ST Motor Control Workbench support for H7A3 in STM32 MCUs Motor control

- Incorrect Symbol Names for STMCubeMX Generated Project IRQ Handlers in STM32CubeMX (MCUs)

- Debug STLink GDB Server v.1.3.0 - PARSE ERROR: Argument: -cp in STM32CubeIDE for Visual Studio Code (MCUs)

- STM32N657X0 NUCLEO — SAU Configuration issue(TrustZone + RIF configuration issue) in STM32 MCUs Security