- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- ['F446 documentation] SAI clock generator

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

['F446 documentation] SAI clock generator

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-02 02:49 PM

The SAI clock generator subchapter and related comments throughout the SAI chapter are confusing. A complete rewrite would be beneficial, but I doubt anybody is willing to do that. So let me give a couple of simple suggestions:

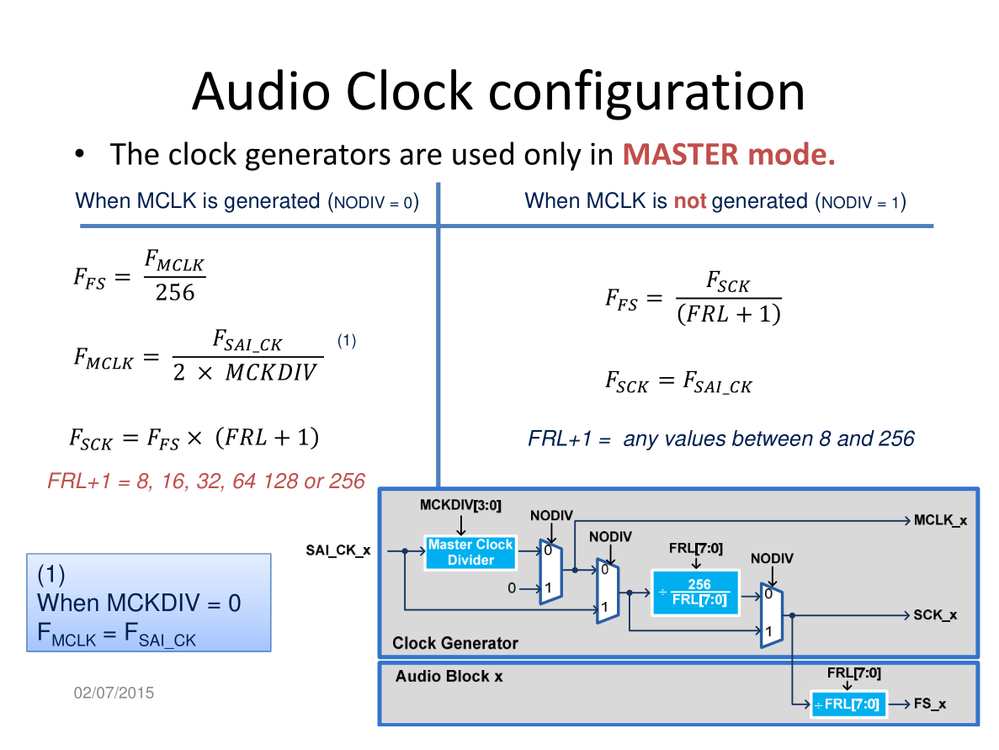

- the figure ought to contain the SCK-to-FS divider; and the MCLK-to-SCK divider should indicate that its division rate is 256/FRL+1; such figure then would present a complete clock information (for free protocol setting + master).

In fact, you already have that figure; I don't see why RM contains an inferior and confusing version:

- similarly, the formula for SCK frequency shall read MCLK/(256/(FRL+1)), as the multiplication form confusingly suggests that there is some ''multiplier'' present; and accompanying text should point out that this strange arrangement is designed so that FS is always MCLK/256. The confusing ''In the SAI, the single ratio MCLK/FS = 256 is considered.'' sentence could then be removed

- the text ''In master mode it is mandatory that (FRL[7:0] +1) is equal to a number with a power of 2'' should be accompained by pointing out the safeguard mechanism in form of WCKCFG

- MCLK stops to be output when MCKDIV=0 and FRL=255; the RM shall say this either in this subchapter, or at FRL bits description; or maybe both, as it's quite surprising.

- in Configuration register 1 (SAI_ACR1 / SAI_BCR1) , description of MCKDIV contains an incorrect formula (the result is not F

SCK_x

)JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-16 03:55 AM

To the last item: that formula is incorrect for FREE, but may be correct for SPDIF; however, it should explicitly say so.

https://community.st.com/0D50X00009XkaCESAZ

JW

- STM32H573: ETH SWRESET fails, ETH_DMAMR_SWR stays set, timeout in STM32 MCUs Embedded software

- Getting Startet with STM32WL33 on CubeIDE, no Data output to Pin in STM32 MCUs Wireless

- Configure peripherals after sleep in STM32 MCUs Embedded software

- STM32U083 LCD Controller generates unexpected High Voltage (5V) - and kills its own GPIO pins in STM32 MCUs Products

- Generate 2MHz SAI Clock for PDM Microphone Using STM32G473VET6 in STM32 MCUs Products