- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- External clock generation at non-multiple of syste...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

External clock generation at non-multiple of system clock

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-04-08 12:24 AM

Hi All,

I am trying to produce a 256 kHz frequency clock for use with audio codecs. I am trying to produce this 256kHz freq from the 120MHz system clock on the STM32F207 series. I would like to use the timers to produce this 256kHz clock, however 256kHz does not evenly divide into 120MHz. (120Mhz/256kHz = 468.75) Does anyone know of a way to produce a non-multiple of the system clock by using a combination of timers, and cascading timers. I have found one way to produce 192MHz from the I2S PLL, and then output on MCO 6.4MHz, which can then be divided down to 256KHz, but this requires two pins, 1 for the MCO pin and 1 for external clock input. I would prefer to be able to just use internal timers and get back two micro controller pins. Any help find a solution to this would be great. #fitter #external-clock #advanced-timers #clocks #magic-crystals #doughnuts- Labels:

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-04-08 3:41 AM

The way the STM32 dividers and counters work you need to use integer factors.

You might have to choose magic crystal values, or PLL combinations, and run the part and non-optimal speeds. With a PCM based design requiring 256 KHz and 8 KHz, I had to run the F103 at 64 MHz. Your option would be to run at 96 MHz, I didn't run all the combinations but this factored and would permit USB operation. 256000 * 375 = 96000000Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-04-08 6:39 AM

> Does anyone know of a way to produce a non-multiple of the system clock

> by using a combination of timers, and cascading timers. I could visualize a one-timer solution involving DMA to dynamically change the reload value, if your application can cope with the resulting jitter. > I have found one way to produce 192MHz from the I2S PLL, and then output on MCO 6.4MHz, You could (ab)use one of the I2S modules as a divider. JW- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-04-08 7:06 AM

The LSE could use a 256 or 512 KHz crystal.

The HSE could use a 8.192 MHz or 16.384 MHz crystal. On the STM32F4 you could run at 128 MHz, or 160 MHzUp vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-04-08 7:22 AM

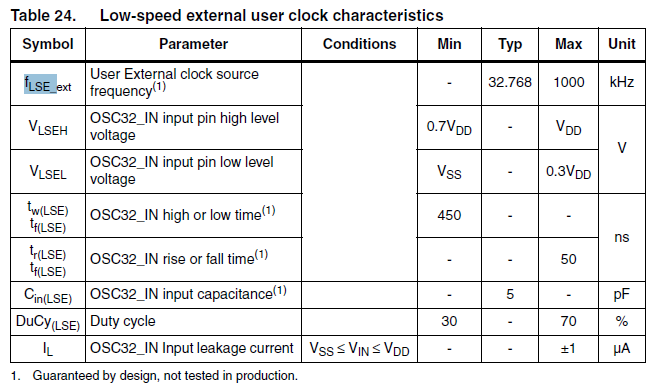

> The LSE could use a 256 or 512 KHz crystal.

Inventive, although... I can't find any information on the capability of the LSE circuitry to drive anything other than a 32.768kHz crystal... JW- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-04-08 7:31 AM

Connectivity via MCO, TIM5 and TIM11

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-04-08 7:47 AM

It's not a coincidence that this table is found under ''Low-speed external user clock generated from an external source'' header.

I'd be very surprised if this would constitute a guarantee that the LSE circuitry can drive a 512kHz crystal. JW- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-04-08 7:47 AM

Making better use of the extra post generated by crappy forum software: I just had a look at AN2867.

The Revision history has this to witness: 17-Jul-2012 - [revision]6 - Whole document restricted to STM32F1 devices. JW- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-04-08 8:37 AM

Honestly, I don't know if the internal Pierce oscillator circuit can be abused in this fashion, or if an external oscillator source is the way to go. I don't have any Pierce targeted 512 KHz crystals to hand (or 256, 768), so probably not something I'm going to experiment with.

Again this reflects on the lameness of the clocking scheme in the part, as I think most lower frequency applications would be fine with 4-9 ns of jitter from an NCO clocked by the VCO or PLL.Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-04-08 9:19 AM

100% agree, but wouldn't in this particular case (relatively high divider) the scheme I outlined above (timer compare value reloaded by DMA triggered by the same compare, alternating between N and N+1) yield the same result than a NCO?

JW- Stm32h743iit6 preload at boot image background using LibJPeg in STM32 MCUs Embedded software

- PWM input output drift in STM32 MCUs Products

- STM32G431 Bootloader issue in STM32 MCUs Products

- STM32C092GCU6: FDCAN interrupt handler name mismatch in STM32CubeMX (MCUs)

- TouchGFX Application Shows Black Screen After Bootloader Jump in STM32 MCUs TouchGFX and GUI