- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: DTCM and SRAM parallel access

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

DTCM and SRAM parallel access

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-08 06:49 AM

Hey everyone,

I'm using a STM32f722ZE.

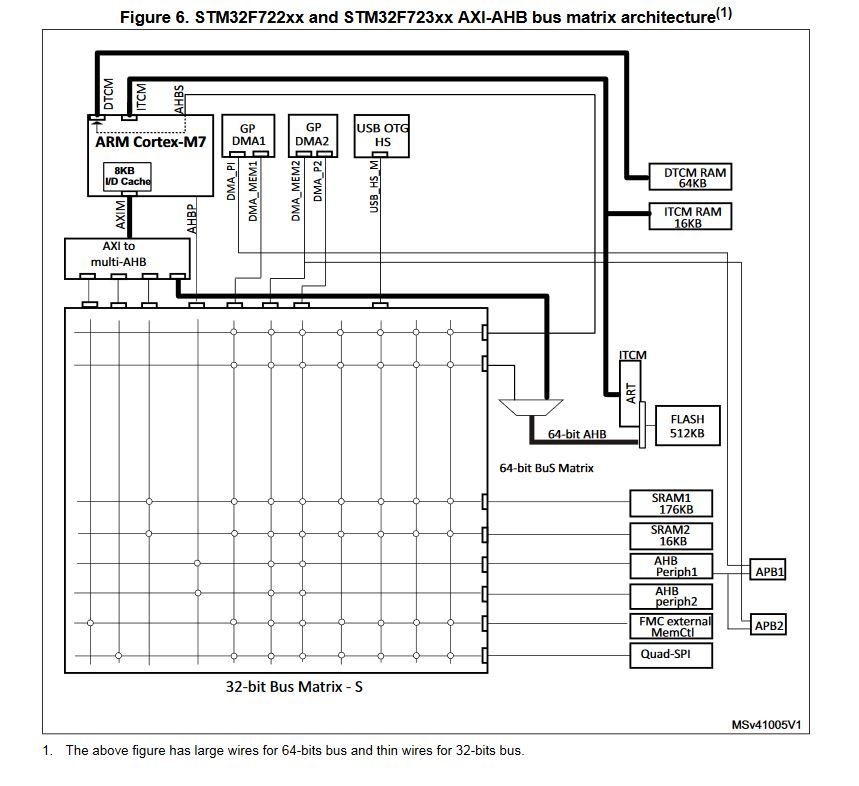

I wanted to know if I allocate two 32KB buffers. One being in SRAM1 and the other in DTCM, With a double buffer DMA2, can the CPU and DMA run in parallel? To my understanding they can. So as soon as the buffer is filled in SRAM2, the DMA will shift to fill the buffer in DTCM and the CPU can process the data in SRAM2. Then the can sort of do this handshake while avoiding collisions on the bus.

Same thing with AHB1 and AHB2, the DMA2 can access AHB1, while the CPU accesses AHB2, all in parallel?

This is my understanding of the busmatrix. The collisions in requests only occur when the same space in the bus is accessed, i.e. Both targeting AHB1 .

Thanks in advance for any clarification

dtcm stm32f7-dma bus-matrixSolved! Go to Solution.

- Labels:

-

STM32F7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-08 06:53 AM

Yes, that's the point of the bus matrix.

Don't forget, that the CPU needs some RAM not only as buffer for your processes but also for variables and stack. DTCM is fast; I am not sure it's a good idea to move stack out of it for sake of some other process.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-08 06:53 AM

Yes, that's the point of the bus matrix.

Don't forget, that the CPU needs some RAM not only as buffer for your processes but also for variables and stack. DTCM is fast; I am not sure it's a good idea to move stack out of it for sake of some other process.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-08 07:54 AM

Perfect, Thanks JW!

Just wanted to be sure I'm not misunderstanding anything

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-08 08:05 AM

Should I just check how much space is reserved in the DTCM for variables and stack or is this a dynamic process that occurs as memory is required?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-08 09:15 AM

The value of the DTCM RAM is that it avoids cache coherency issues, so the processor always pulls directly.

To use other SRAM you need to either mark it as uncacheable or invalidate after DMA has changed the content behind the cache.

>>

can the CPU and DMA run in parallel

Ok, to repeat what has been communicated in other threads, contention does not preclude multiple use, operations will be deferred and arbitrated.

Change the mindset from parallel/simultaneously to sequenced/ordered, the hardware is designed to permit concurrent operation in an orderly manner, to the point where you exhaust available bandwidth/channels at which point it will grind along as best it can.

Stacks are best in TCM, but caching should mask slower memories.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-08 09:31 AM

Or would a buffer in SRAM1 and SRAM2 be better?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-10 04:26 AM

Hi Clive,

Thank you.

>>

can the CPU and DMA run in parallel

Ok, to repeat what has been communicated in other threads, contention does not preclude multiple use, operations will be deferred and arbitrated.

Change the mindset from parallel/simultaneously to sequenced/ordered, the hardware is designed to permit concurrent operation in an orderly manner, to the point where you exhaust available bandwidth/channels at which point it will grind along as best it can.

This was a bit of a mindset shift, but I completely understand now.

Thanks for all the help thus far!

- STM32H735IGK6 SRAM and Flash Speed in STM32 MCUs Products

- NMI Fault without any obvious fault bits set in STM32 MCUs Embedded software

- PSSI and DMA issue in STM32 MCUs Products

- FMC does not trigger Write Enable on SRAM in STM32 MCUs Products

- STM32N6 H264 encoder motion vectors in STM32 MCUs Products