- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- DFSDM sinc filter STM32H743 Problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

DFSDM sinc filter STM32H743 Problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-30 2:22 AM - edited 2023-10-30 2:23 AM

Hello,

I am trying to use the DFSDM module on the Nucleo-H743ZI2 board .

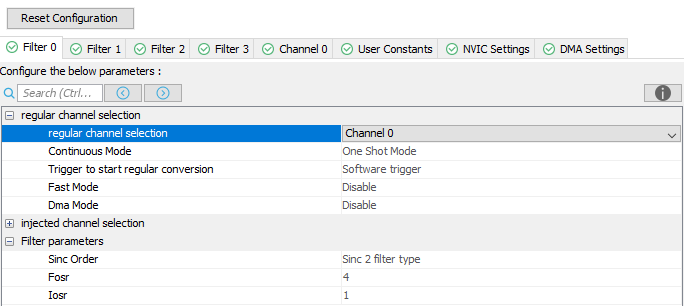

As a minimal example, i tried to use a sinc filter of 2. order with a FOSR of 4.

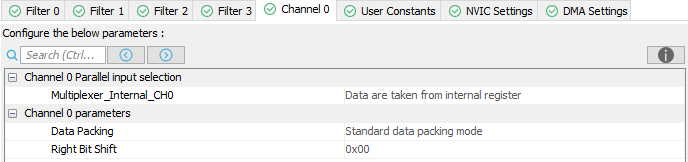

Channel0 is activated in the parallel mode, standard data packing mode and the setting to take data from internal register.

Additionally I mapped Filter0 to Channel0 and set it in one shot mode, software triggered, fastmode disabled, DMA disabled and setup the sinc filter parameter as mentioned before.

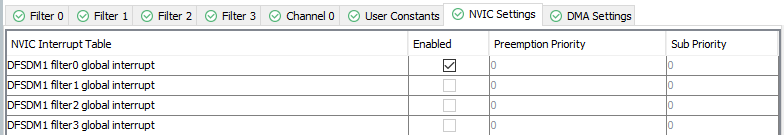

Finally enabled the global interrupt for Filter0.

Afterwards i generated the Code and crosschecked the parameters in the MX_DFSDM1_Init:

static void MX_DFSDM1_Init(void)

{

hdfsdm1_filter0.Instance = DFSDM1_Filter0;

hdfsdm1_filter0.Init.RegularParam.Trigger = DFSDM_FILTER_SW_TRIGGER;

hdfsdm1_filter0.Init.RegularParam.FastMode = ENABLE;

hdfsdm1_filter0.Init.RegularParam.DmaMode = DISABLE;

hdfsdm1_filter0.Init.FilterParam.SincOrder = DFSDM_FILTER_SINC2_ORDER;

hdfsdm1_filter0.Init.FilterParam.Oversampling = 4;

hdfsdm1_filter0.Init.FilterParam.IntOversampling = 1;

if (HAL_DFSDM_FilterInit(&hdfsdm1_filter0) != HAL_OK)

{

Error_Handler();

}

hdfsdm1_channel0.Instance = DFSDM1_Channel0;

hdfsdm1_channel0.Init.OutputClock.Activation = DISABLE;

hdfsdm1_channel0.Init.OutputClock.Selection = DFSDM_CHANNEL_OUTPUT_CLOCK_SYSTEM;

hdfsdm1_channel0.Init.OutputClock.Divider = 2;

hdfsdm1_channel0.Init.Input.Multiplexer = DFSDM_CHANNEL_INTERNAL_REGISTER;

hdfsdm1_channel0.Init.Input.DataPacking = DFSDM_CHANNEL_STANDARD_MODE;

hdfsdm1_channel0.Init.Input.Pins = DFSDM_CHANNEL_SAME_CHANNEL_PINS;

hdfsdm1_channel0.Init.SerialInterface.Type = DFSDM_CHANNEL_SPI_RISING;

hdfsdm1_channel0.Init.SerialInterface.SpiClock = DFSDM_CHANNEL_SPI_CLOCK_EXTERNAL;

hdfsdm1_channel0.Init.Awd.FilterOrder = DFSDM_CHANNEL_FASTSINC_ORDER;

hdfsdm1_channel0.Init.Awd.Oversampling = 1;

hdfsdm1_channel0.Init.Offset = 0x00;

hdfsdm1_channel0.Init.RightBitShift = 0;

if (HAL_DFSDM_ChannelInit(&hdfsdm1_channel0) != HAL_OK)

{

Error_Handler();

}

if (HAL_DFSDM_FilterConfigRegChannel(&hdfsdm1_filter0, DFSDM_CHANNEL_0, DFSDM_CONTINUOUS_CONV_OFF) != HAL_OK)

{

Error_Handler();

}

}

Then I added the callback interrupt routine where I put the result of the actual completed conversion in the buffer dac_out:

void HAL_DFSDM_FilterRegConvCpltCallback(DFSDM_Filter_HandleTypeDef *hdfsdm_filter)

{

uint32_t channel = 0;

dac_out[i] = HAL_DFSDM_FilterGetRegularValue(hdfsdm_filter, &channel);

HAL_DAC_SetValue(&hdac1, DAC_CHANNEL_1, DAC_ALIGN_12B_R, dac_out[i]);

if(i<buff_size)

{

i++;

} else {

i=0;

}

}

In the main while(1) loop i added two rows of code to start regular filter conversion IT and put the value that has to be converted in the DFSDM channel data input register CHDATINR of Channel0.

while(1)

{

HAL_DFSDM_FilterRegularStart_IT(&hdfsdm1_filter0);

DFSDM1_Channel0->CHDATINR = data_in[i];

}

The converted results are not as i thougth they would be.

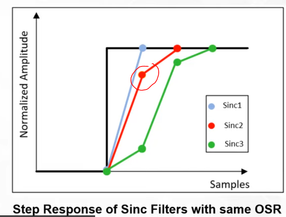

For example when giving constantly the value 1000 to convert, I would expect that the filter output reach the value 1000*FOSR^Order = 16000 after two sample cycles like illustrated in this graph:

That is not the case. I am missing the data point before reaching the final value 16000.

In addition, if I raise the filter order the output values are also jumping always from zero directly to final value without having the steps in between...

Can someone help me in figuring out what I am missing?

Thanks

- Labels:

-

DFSDM

-

STM32H7 Series

- STM32H743 SDMMC handling timeouts -- problem with IDMA control register in STM32 MCUs Products

- Programming STM32H743 Nucleo-144 with with ST-link2 in STM32 MCUs Boards and hardware tools

- External loader issue with STM32H743 and W25Q512 in STM32CubeProgrammer (MCUs)

- STM32H743 SPI Master works fine... problem is it should fail :) in STM32 MCUs Embedded software

- timer 3 channel 2 pwm influence channel 4 in STM32 MCUs Products