- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Connection between ADC Clock and sample rate

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Connection between ADC Clock and sample rate

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-23 6:44 AM

Hello all,

I am a beginner in the world of STM32 programming and need a little help with the ADCs.

I am currently using the STM32H735IG Discovery Kit and CubeIDE.

For an ongoing project I am using the ADC1 to sample channel IN0.

The DMA and sampling is working fine, but i am not sure how to set up the clockrate of the ADC properly.

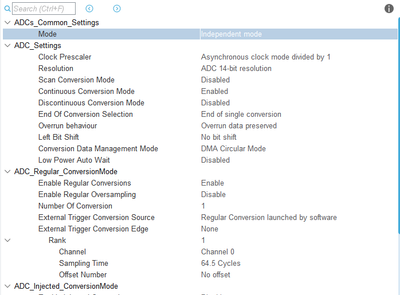

The ADC is currently running in Asynchronous mode with divider 1 and the sampling time is set to 64,5 Cycles.

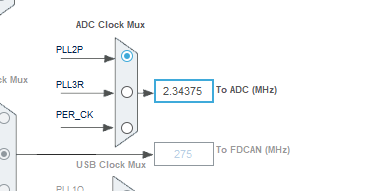

The clock rate of the ADC is currently set to 2.34375 MHz in the Clock Configuration.

Currently i store 16 samples in my DMA buffer:

HAL_ADC_Start_DMA(&hadc1, (uint32_t*) ADC_DMA_buffer, 16);

To monitor if the the ADC is working fine I am toggling an LED on the discovery board and monitor the signal with an Oscilloscope.

void HAL_ADC_ConvCpltCallback(ADC_HandleTypeDef* hadc)

{

HAL_GPIO_TogglePin(GPIOC, GPIO_PIN_3);

}

With the current settings I can measure a frequency of 17,36 kHz on my LED.

This value times 16 samples times 2 toggles for one pulse, should be the actual sample rate of the ADC.

Now to the problem:

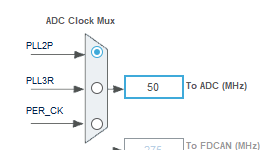

When I increase the clock frequency of the AD converter, to lets say 50 Mhz, the sample rate does not change

and I don't know why. The LED has still the same frequency of 17,36 kHz. Is there something I am missing?

In my imagination I thought the clock frequency should directly relate to the sampling rate of the ADC.

I hope someone can help me with this problem.

Thanks and best regards,

Dennis

- Labels:

-

ADC

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-23 7:05 AM - edited 2023-08-23 7:07 AM

The cpu is overloaded and can't keep up with the rate at which interrupts are triggered.

Increase the number of samples to 2000 and try it again.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-23 7:19 AM

Hi,

thanks for your answer.

I don't think the CPU usage is the problem.

When i reduce the sample time to 1,5 Cycles, i can even measure a frequency of over 138 kHz at my control LED.

Best regards,

Dennis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-23 7:57 AM

The ADC does 1 conversion in (sample cycles+bit resolution+3) clock cycles.

The ADC conversion time is then conversion clock cycles/clock frequency.

Your ADC conversions are software triggered, so the sample rate is determined by whatever frequency your app is able to start the conversion, which is what TDK is referring to.

I wish we would change the term Sample Cycles to PreConversion Cycles, to avoid confusion.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-23 8:00 AM

Probably the ADC clock is not actually changed then. Are you regenerating the code?

Call HAL_RCCEx_GetPLL2ClockFreq and verify it returns the expected value.

Looks like your ADC clock is 40 MHz based on your LED frequency, maybe 80 MHz. Does that ring a bell?

17.36kHz*2*(64.5+7.5)*16 = 39997440 Hz

138kHz*2*(1.5+7.5)*16 = 39744000 Hz

Could be I'm missing something else but not sure what it would be.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-23 12:20 PM

Sampling Time and Sampling Rate is not related to each other director.

Sampling time is base on ADC Clock speed and how many clock does it use in conversation which ADC Clock you can set it on clock configure.

Sampling Rate is base on how many trigger does it happen in a second which you can set it by Extrenal Trigger to choose how you can control it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-23 11:08 PM - edited 2023-08-24 5:59 AM

Hi TDK,

When i change something in the ioc file with the CubeMX view i click on save all -> Generate Code? -> Yes -> Build (Hammer Icon) -> Run (Green Play Icon).

For the HAL_RCCEx_GetPLL2ClockFreq function you mean like this, right?

Here is an overview of my clock settings, it don't really know what causes the wrong ADC clock frequency...

@raptorhal2The ADC is only triggered once in software, then it is running in "Continous Conversion Mode" with active "DMA Circular Mode". What is limiting the sample rate with this setup?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-24 6:24 AM

Yes, and do the values in pll2_clocks match what you expect?

If they do, not really sure what it could be.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-24 6:54 AM

Hi TDK,

unfortunately i couldn't figure out how to properly set up the continuous conversion mode.

I couldn't macht up my expected sampling rate with the real measured sampling rate.

Now I have switched over to a timer based ADC trigger input, which works fine so far.

Maybe i will try to understand the continuous mode on a later point in time.

Anyway, thanks for your help.

Best regards,

Dennis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-25 12:55 AM

Hello,

maybe I was a little bit to quick.

Even with the Timer triggering the ADC, the ADC Clock frequency has no visible influence and I don't know why.

Currently I am generating a 500 kHz PWM signal from a Timer to trigger my ADC.

I also have mapped the signal to a Output-Pin, so I can monitor the signal, which works fine.

I am still using my DMA function like before, but now with 25 samples, which i am averaging down to a single data point signal with 20kHz sample rate.

HAL_ADC_Start_DMA(&hadc1, (uint32_t*) ADC_DMA_buffer, 25);With 14-Bits (7.5 Cycles) and an acquisition time of 64.5 Cycles this should calculate to a minimum ADC Clock Frequency of 500k * (7.5+64,5) = 36 MHz.

But even if I lower the ADC clock to the lowest possible 2.34375 MHz in den CubeMX clock configuration, I still get my 20kHz output from my ADC, which should not be possible?

Is there something I am missing?

- read multiple samples from adc each 10 seconds with dma in STM32 MCUs Products

- Beaconing advertisement in STM32 MCUs Wireless

- Failed to execute MI command STM32WBA5 in STM32 MCUs Products

- FMC to connect external SDRAM. Do I need length or impedance matching? in STM32 MCUs Products

- DTM test for RF testing (Enable DTM Mode for BLE-SPBTLE-RF0 via SPI1 on STM32L053) in STM32 MCUs Products