- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Calculate external capacitors CL1 and CL2 for ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Calculate external capacitors CL1 and CL2 for crystal oscillator

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-15 8:02 AM

Hello everyone,

I'm writing to raise awareness of a potential problem with quartz resonators that could affect clock designs.

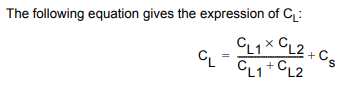

In your AN2867, you provide a formula for calculating the load capacitances of quartz oscillators.

The datasheet for the STM32L431 states that 10 pF can be used as an approximate estimate of the total capacitance of the contacts and board. Does this mean that the quartz must have a nominal load capacitance greater than 10 pF?

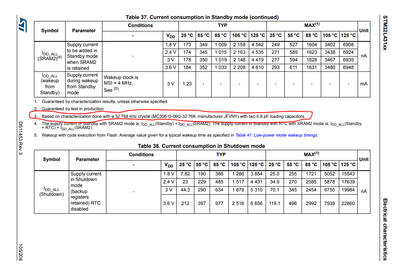

If the answer is yes, then why is the quartz MC306-G-06Q-32.768 with a CL=6 pF parameter, which is additionally loaded with capacitances of 6.8 pF, used for power consumption measurements in the datasheet?

Please share your thoughts in the comments below.

Thanks,

Maksym

Solved! Go to Solution.

- Labels:

-

STM32L4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-19 2:13 AM

Hello,

your question is mixing LSE and HSE crystal. However, I need to say that 10pF mentioned in DS is too much and would be better not include any number in DS regarding this matter (as it depends on package, layout,.. tolerance PCB).

From our experiences the parasitic capacitance Cs = given IO and layout is ~2pF typically (1.5 - 4 pF range).

In case when we se 6pF Cload crystal option and populated with 6.8pF external padded capacitors means that parasitic is roughly 2.6pF ( =6 - 6.8/2).

Crystals which are designed for 6pF Cload are supported by L4 family.

In terms of correct capacitor selection it’s not only about layout but also IO capacitance.

Unfortunate IO capacitance is not characterized deeply, so 5pF is for informative purpose only. There are missing min. max values and there is no plan to validate them. For HSE input/output circuitry may be different.

It's better to measure freq on first PCB release/prototype sample via MCO pin (available on PA8 + others depends on device and package size). Measuring must be done by counter or by scope with averaging (or in counter mode) to avoid short term jitter. And then tune external capacitors accordingly to get nominal crystal frequency.

fmeas > fnom … increase external capacitors

fmeas < fnom … decrease external capacitors

BR, Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-15 8:24 AM

> Does this mean that the quartz must have a nominal load capacitance greater than 10 pF?

If it were true, yes.

> If the answer is yes, then why is the quartz MC306-G-06Q-32.768 with a CL=6 pF parameter, which is additionally loaded with capacitances of 6.8 pF, used for power consumption measurements in the datasheet?

These calculations are not exact. In the context of selection load caps, 10 pF is approximately 6 pF, and the board chosen can affect things.

Tolerances on the load caps are generally forgiving. Use 6 pF and if it doesn't work, venture further away. It can be a science if you want it to be, and you have sensitive equipment to measure these sorts of things, but most people will use the educated guess trial and error method.

I have not seen 10 pF been given as an estimate and always use ~6 pF as the estimate myself. Your mileage may vary.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-19 2:13 AM

Hello,

your question is mixing LSE and HSE crystal. However, I need to say that 10pF mentioned in DS is too much and would be better not include any number in DS regarding this matter (as it depends on package, layout,.. tolerance PCB).

From our experiences the parasitic capacitance Cs = given IO and layout is ~2pF typically (1.5 - 4 pF range).

In case when we se 6pF Cload crystal option and populated with 6.8pF external padded capacitors means that parasitic is roughly 2.6pF ( =6 - 6.8/2).

Crystals which are designed for 6pF Cload are supported by L4 family.

In terms of correct capacitor selection it’s not only about layout but also IO capacitance.

Unfortunate IO capacitance is not characterized deeply, so 5pF is for informative purpose only. There are missing min. max values and there is no plan to validate them. For HSE input/output circuitry may be different.

It's better to measure freq on first PCB release/prototype sample via MCO pin (available on PA8 + others depends on device and package size). Measuring must be done by counter or by scope with averaging (or in counter mode) to avoid short term jitter. And then tune external capacitors accordingly to get nominal crystal frequency.

fmeas > fnom … increase external capacitors

fmeas < fnom … decrease external capacitors

BR, Jan

- Schematic Review Request for Custom Board Based on MB1389E in STM32 MCUs Wireless

- STM32WLE5CCU7 - Can't make HSE work on custom board in STM32 MCUs Wireless

- What is the actual STM32 pin capacitance (for the purpose of sizing an HSE crystal)? in STM32 MCUs Products

- STM32F411 HSE Ceramic Resonator external resistor value in STM32 MCUs Products

- Input capture / Frequency Measurement error on STM32U545REQ in STM32 MCUs Products