- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Backup SRAM content lost in VBAT-mode

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Backup SRAM content lost in VBAT-mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-28 03:09 AM

Are VCAP_1 and

VCAP_2 used in Vbat-mode?

I have an issue with the content of the Backup SRAM is lost when i power down the device, even though the Vbat is active.

If i do a reset the content of backup SRAM and RTC-registers remain. But if i remove Vdd for a few ms the content of the backup SRAM becomes garbage but the

RTC

-registers are not affected.

I have checked with an oscilloscope that the voltage at Vbat never drops below 3.1 Volts.

I have enabled the backup regulator with a call to 'HAL_PWREx_EnableBkUpReg()'. I have also checked that the BRE and BRR flags gets set in the PWR->CSR register.

My theory that i hope someone can confirm or discard:

Backup SRAM does not work in 'BYPASS_REG'-mode.

I use my own 1.2Volt regulators connected to VCAP_1 and

VCAP_2

and have pin 'BYPASS_REG' hardwired to 3.3 Volts in normal mode.When i power down Vdd,

VCAP_1,

VCAP_2

and BYPASS_REG are pulled low.

After a power cycle the 'Backup regulator enable' in register 'PWR power control/status register' is still set, but the 'Backup regulator ready' takes some time before it becomes set. I believe this indicates that there is some issue with the power...

I use a STM32F429

#stm32f429 #sram-backup-rtc #bypass_reg- Labels:

-

RTC

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-28 03:30 AM

How's your VCAP1, 2 -- PA0 -- NRST sequencing, up and down?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-01 12:05 AM

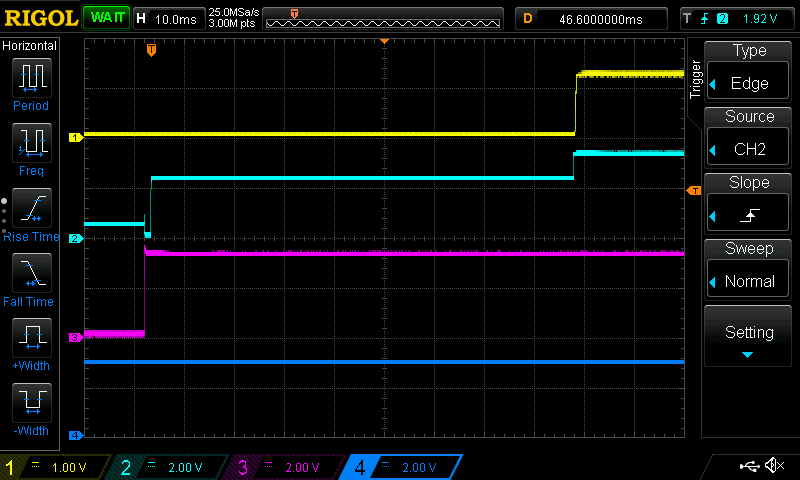

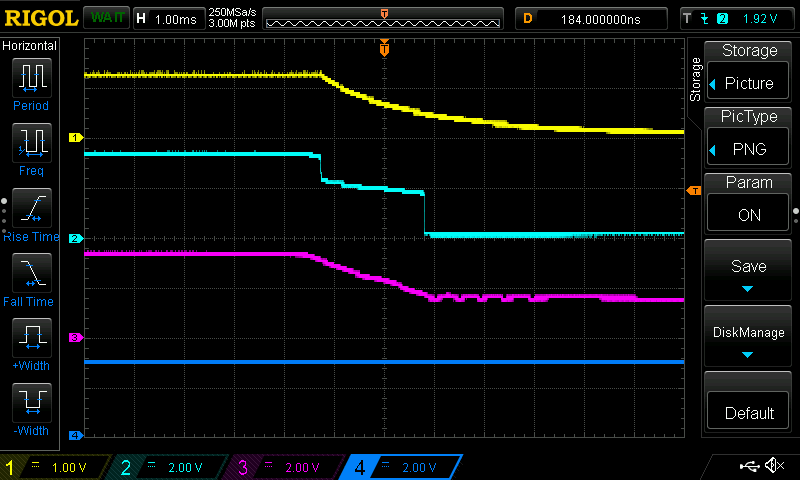

Here are the startup and shutdown sequence.

Ch1-Yellow: 1.2V connected to Vcap_1 and

Vcap_2

Ch2-Cyan: NRST (PA0)

Ch3-Purple: 3.3V connected to Vdd.

Ch4-Blue: VBAT

Startup (100ms recording)

Shutdown (10ms

recording

)- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-01 03:23 AM

Then this is the problem.

You MUST hold both reset and PA0 low long enough until V12 and VDD gets stable, and you must pull them low soon enough when they start to fall.

See the Startup in regulator OFF mode: fast V DD slope- power-down reset risen before V CAP_1 /V CAP_2 stabilization figure in DS.

JW

- How do STM32H753XIH6 and STM32L4S7AII6 verify memory contents? in STM32 MCUs Products

- Functional Safetey U5 Series in STM32 MCUs Products

- Micro without VBAT pin - detect 'Main' or 'Backup' power in STM32 MCUs Products

- Implementing STM32L4S5ZIT6 Bootloader with a Memory Marker in STM32 MCUs Products

- STM32H7 HW CS unexpected set inactive during SPI transfer in STM32 MCUs Products