- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Are STM32L0 FT pins 5V tolerant in Analog mode whe...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Are STM32L0 FT pins 5V tolerant in Analog mode when no Analog peripheral is enabled?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-16 3:21 PM

Many ST documents says that FT pins are 5V tolerant only in (Digital) Input mode. They are not 5V tolerant when configured in Analog mode and analog peripheral like ADC or OPAMP is connected to it. But are they 5V (or more precisely Vdda + 3.6V tolerant) when configured in Analog mode, but no peripheral is connected to it?

In AN4899, there are many indications that they are, but I did not find it explicitely speficied anywhere. Some paragraphs indicating are:

Background:

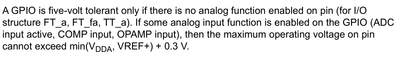

My idea is using STM32L053 powered by 2.0V and I need to measure analog voltage which ranges from 0 - 2.25V when MCU is not powered (VDD=0.0V) and between 2.0 - 5.4V when MCU is powered (VDD=2.0V). For lowering voltage I will use voltage divider which divides voltage by approximately 3. But this voltage divider cause power consumption which is unacceptable in my design. For lowering power consumption as much as possible I need to cut off it for most time. I want to connect it similarly to Figure 14 from AN4899, but instead of using internall pull down I will use externall and it will not be pull-down but rather "pull-open-drain-down". My idea is following:

When ADC will be in progress, FT GPIO2 will be held low and will act as ground. Current will flow from high-voltage source through R1 and R2 to FT GPIO2. Voltage on FT GPIO1 will be reduced by voltage divider to safe level and will be measured by ADC.

When ADC will not be in progress, both FT GPIO1 and 2 will be in Analog mode (High impedance with Schmidt trigger disabled) and ADC will be disconnected from ADC (channel will be disabled). Becase both pins are Hi-Z, current can't flow through them and voltage divider will not cause power consumption anymore. But resistors will not drop voltage and both pins FT GPIO1 and 2 will be exposed to high voltage. Here my question come in: Are FT pins 5V tolerant in this situation? Pins are in Analog mode with deteched all analog peripherals, but not in Input mode. I can't use Input mode because it remains Schmidt trigger enabled which will cause additional power consumption when analog voltage will be at the transition of 0/1 logic level.

Of course I will need to correctly manage transitions between states and manage to change GPIO modes and attach/detach ADC in right order.

Solved! Go to Solution.

- Labels:

-

ADC

-

STM32L0 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-17 4:36 AM

Dear @misaz ,

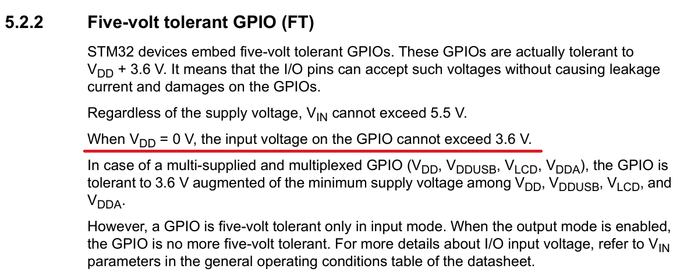

The Answer is Yes ! you can use and keep the FT pin when the I/O is in analog mode. The key information is put in this application note : STM32 microcontroller GPIO hardware settings and low-power consumption - Application note

Section 4.3.4 - Analog configuration :

"The analog switch itself is not closed. The analog switch is closed only when analog peripheral is selected (or enabled) on the given pin."

If the analog switch is closed ( inside the analog peripheral) in our case inside the ADC , we will loose the 5-volt tolerance as a diode will connect to Vin to VDDA/VREF+ .

Please note also, when VDD=0Volts, we can not say or configure the I/O in any mode - input floating or Analog etc. it has no meaning as we not in operational/functional modes, you need to refer to table of voltage Voltage characteristics in the "Absolute maximum ratings" chapter, we should not exceed 4volts as Exposure to maximum rating conditions for extended periods may affect device reliability.

Hope it helps you

Cheers,

STOne-32

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-16 10:59 PM

Dear @misaz ,

First welcome in our Community and thank you for sharing the use case . The question is very clear : If the FT pin feature will be kept when the I/O is just configured in Analog mode to gain the extra leakage from the input shmitt trigger ?

in this STM32L0 series , you can see that we have 3 types of I/O : TC , FT, FTf ( I2C) and VDD + VDDA should be kept on same potentiel . We will be back to you if possible or not ?

Cheers,

STOne-32

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-17 1:50 AM

Hi @STOne-32 ! Thank you for reply.

My question is: If the FT pin will accept input voltage higher than Vdda (and Vdd which is at the same level as Vdda) when configured in Analog Mode (GPIOx_MODER=0b11), internall pull-up and pull-down are disabled (GPIOx_PUPDR=0b00) and all analog peripherals (ADC, DAC, COMP) do not use this pin (ADC_CHSELR=0b0, and so on).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-17 1:56 AM

I did typo when writing my qeustion.

Following sentense:

"When ADC will not be in progress, both FT GPIO1 and 2 will be in Analog mode (High impedance with Schmidt trigger disabled) and ADC will be disconnected from ADC (channel will be disabled)."

Should be:

"When ADC will not be in progress, both FT GPIO1 and 2 will be in Analog mode (High impedance with Schmidt trigger disabled) and ADC will be disconnected from FT GPIO1 pin (channel will be disabled)."

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-17 4:36 AM

Dear @misaz ,

The Answer is Yes ! you can use and keep the FT pin when the I/O is in analog mode. The key information is put in this application note : STM32 microcontroller GPIO hardware settings and low-power consumption - Application note

Section 4.3.4 - Analog configuration :

"The analog switch itself is not closed. The analog switch is closed only when analog peripheral is selected (or enabled) on the given pin."

If the analog switch is closed ( inside the analog peripheral) in our case inside the ADC , we will loose the 5-volt tolerance as a diode will connect to Vin to VDDA/VREF+ .

Please note also, when VDD=0Volts, we can not say or configure the I/O in any mode - input floating or Analog etc. it has no meaning as we not in operational/functional modes, you need to refer to table of voltage Voltage characteristics in the "Absolute maximum ratings" chapter, we should not exceed 4volts as Exposure to maximum rating conditions for extended periods may affect device reliability.

Hope it helps you

Cheers,

STOne-32

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-17 4:47 AM

Hi @STOne-32 . Thank you for answer.

VDD=0V should be ok becase when MCU is not powered, voltage on input will not exceed 2.25V in my case. According to AN4899 this should be safe also:

- TCPP01-M12 + STM32G071 UCPD — C-to-C cable gives no power, A-to-C limited to 5V in STM32 MCUs Boards and hardware tools

- STM32H742 intermittent SD card lockup in STM32 MCUs Embedded software

- USBX Host MSC on Nucleo-H753ZI not recognizing Thumb Drive (HSI48 + CRS configuration) in STM32 MCUs Embedded software

- Unable to activate SAI on stm32h7s78-dk in STM32 MCUs Embedded software

- STM32H757 SDMMC + FATFS consistently returns FR_NOT_READY in STM32 MCUs Embedded software