- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- ADC with DMA in discontinuous mode samples first r...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ADC with DMA in discontinuous mode samples first rank twice (STM32F103)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-03 12:32 AM

Hi,

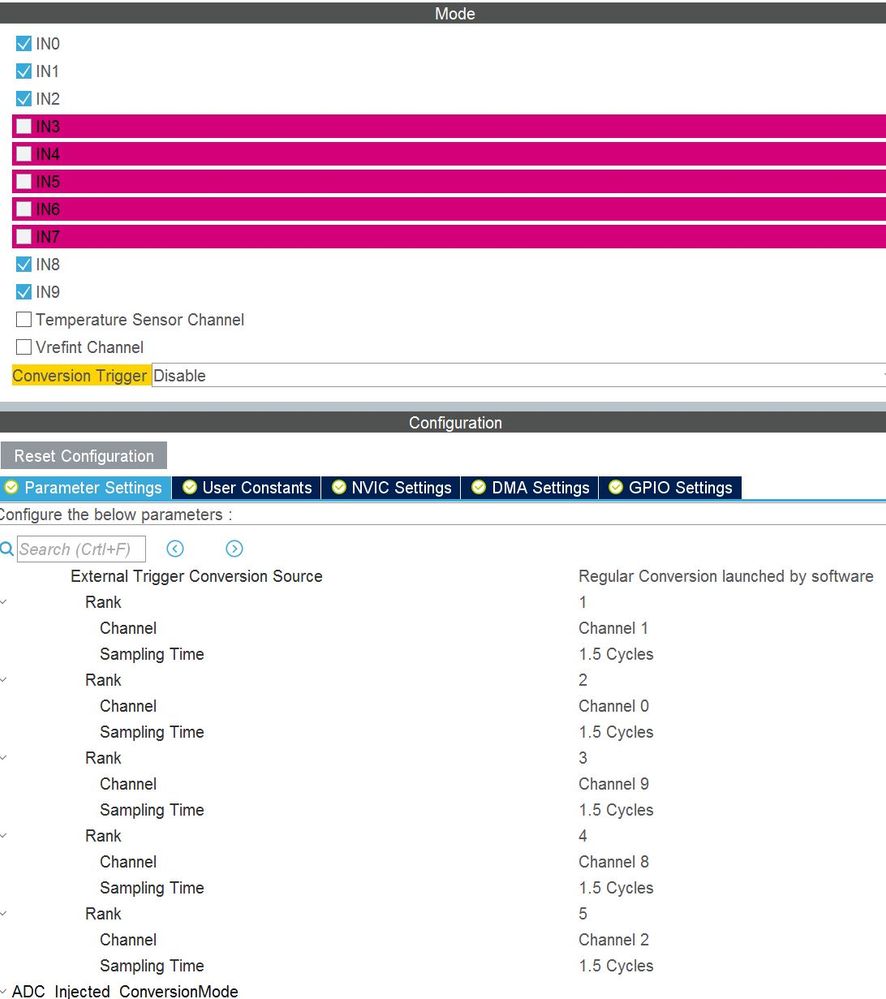

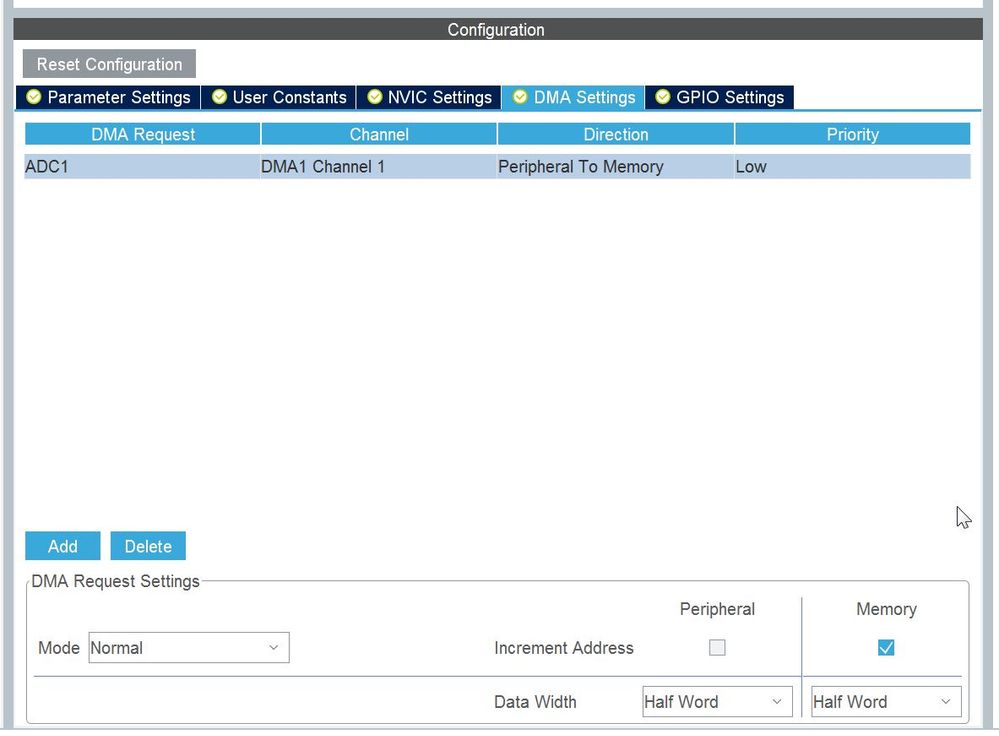

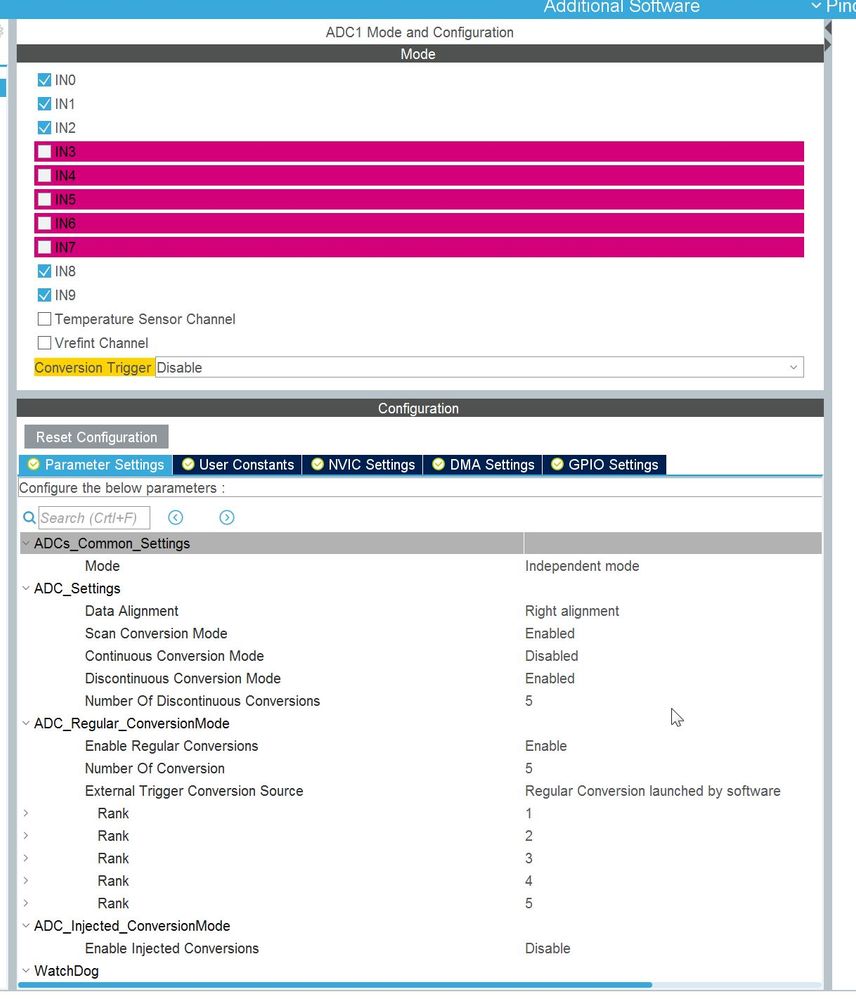

I want to use an ADC with DMA in a STM32F103. I configured it in Cube as you can see in the following picures.

When I start the conversion with

HAL_ADC_Start_DMA(&hadc1,(uint32_t*)AdcData,5);

HAL_ADC_ConvCpltCallback() is called and I see that the AdcData values all changed.

Unfortunately the first rank is sampled twice and the last rank is lost.

I tried to extend the DMA length to 6 but then I do not receive the callback.

I tried to extend the DMA length to 4 but then the last AdcData is unchanged.

Has anybody an idea why this happens and how I can get rid of this?

Solved! Go to Solution.

- Labels:

-

ADC

-

DMA

-

STM32F1 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-09 12:19 AM

I use the Segger tool chain, which is quite reliable.

>>Then I reset all registers of the ADC and DMA to the values they had at the first cycle at exactly this location.

>What exactly do you do? Doesn't this start an ADC conversion?

I set the register values via the register editor in the debugger back to thier earlier values.

So in the second cylce just before the ADC_CR2_DMA bit is set I have the following system state:

- ADC enabled waiting for SW-trigger or DMA request

- ADC_CR2_DMA = 1 ; still set from first ADC sequence cycle (wrong, in my optinition, HAL should disable it when all transactions finished)

- DMA is still enabled (wrong in my optinion; HAL should disable it when all transactions finished)

- DMA_CNDTR0 = 0

Since DMA_CNDTR0 = 0 i assume that there is no DMA request pending. (if it were the ADC would keep konverting).

If I now set the ADC_CR2_DMA bit again the ADC conversion starts.

I just found the follwing note:

ADC_CR2:

Bit 0 ADON: A/D converter ON / OFF ..

1: Enable ADC and to start conversion

Note: If any other bit in this register apart from ADON is changed at the same time, then

conversion is not triggered. This is to prevent triggering an erroneous conversion.

Since the ADC_CR2.ADON bit is in the same register as the DMA bit this rule applies for setting the DMA bit. If the DMA bit was 1 before and is rewritten with 1 again, this might be counted as "DMA bit did not change" which might cause the (also set (correct)) ADON bit to trigger the ADC conversion.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-09 12:46 PM

That sounds as a plausible explanation.

JW

- « Previous

-

- 1

- 2

- Next »

- STM32 and CRA Cyber Resilience Act compliance in STM32 MCUs Security

- STM32F103TBU6 Bare Die / Wafer Availability for R&D Prototyping in STM32 MCUs Products

- STM32H7: jumps in ADC transfer curve; both with Self-calibration, and FactoryLoad in STM32 MCUs Products

- DMA-ADC timed by Tim6 in STM32 MCUs Products

- Stm32f103 samples per second adc in STM32 MCUs Products