- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- ADC with DMA in discontinuous mode samples first r...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ADC with DMA in discontinuous mode samples first rank twice (STM32F103)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-03 12:32 AM

Hi,

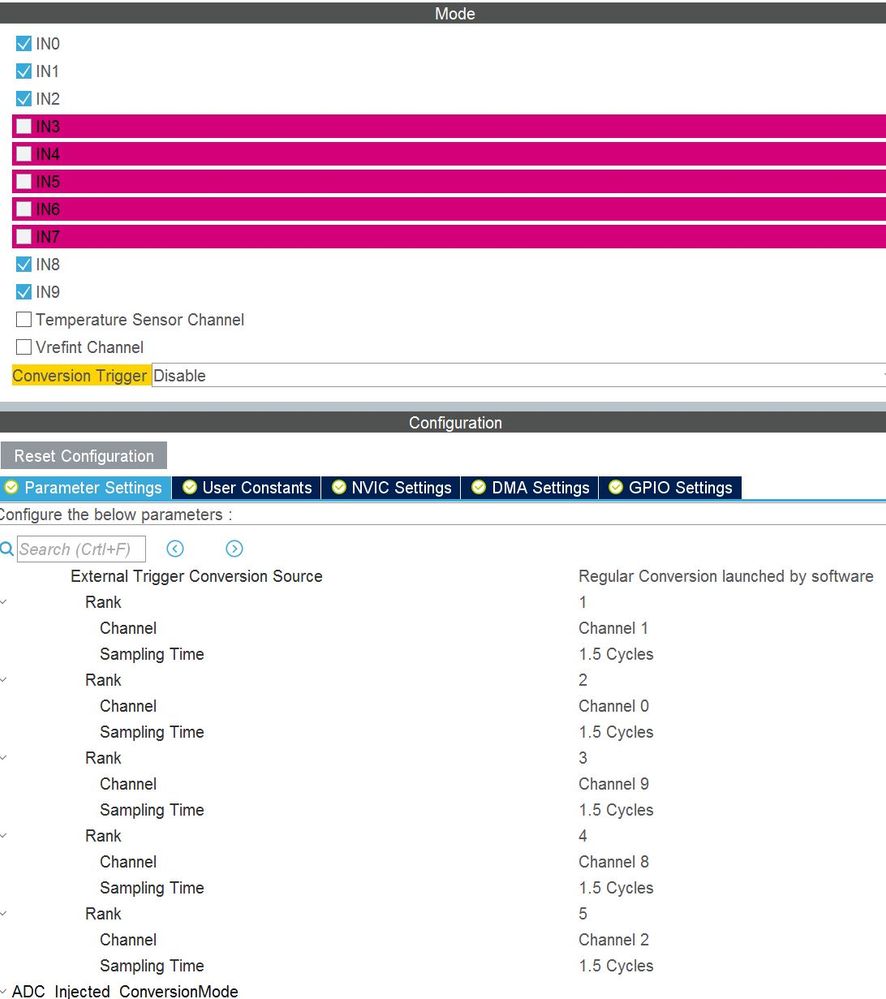

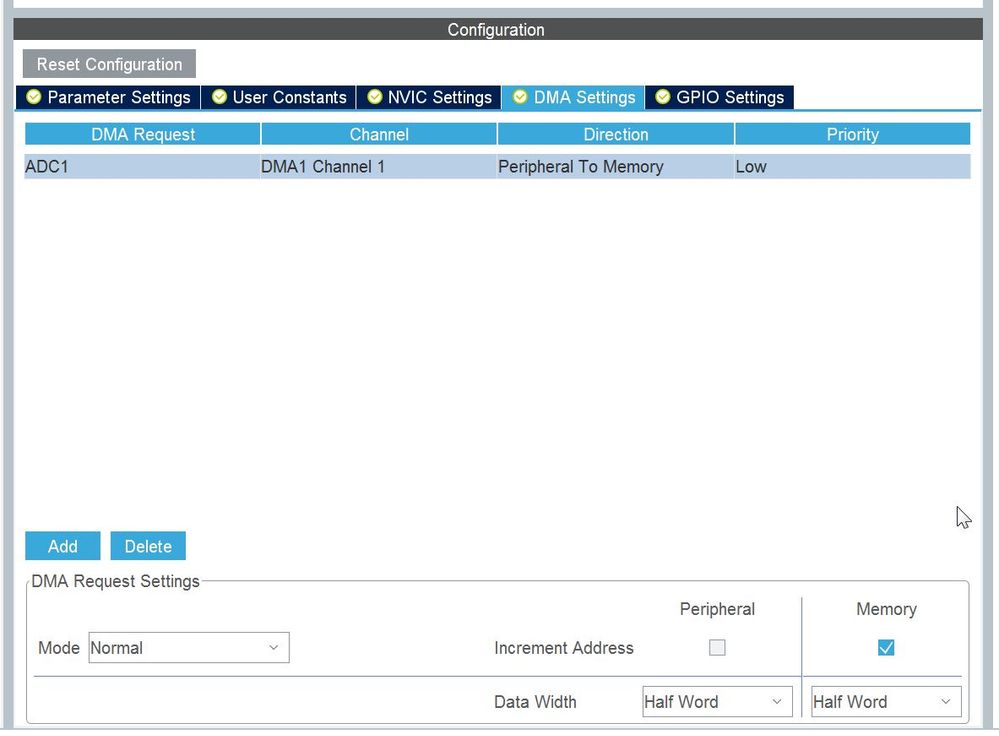

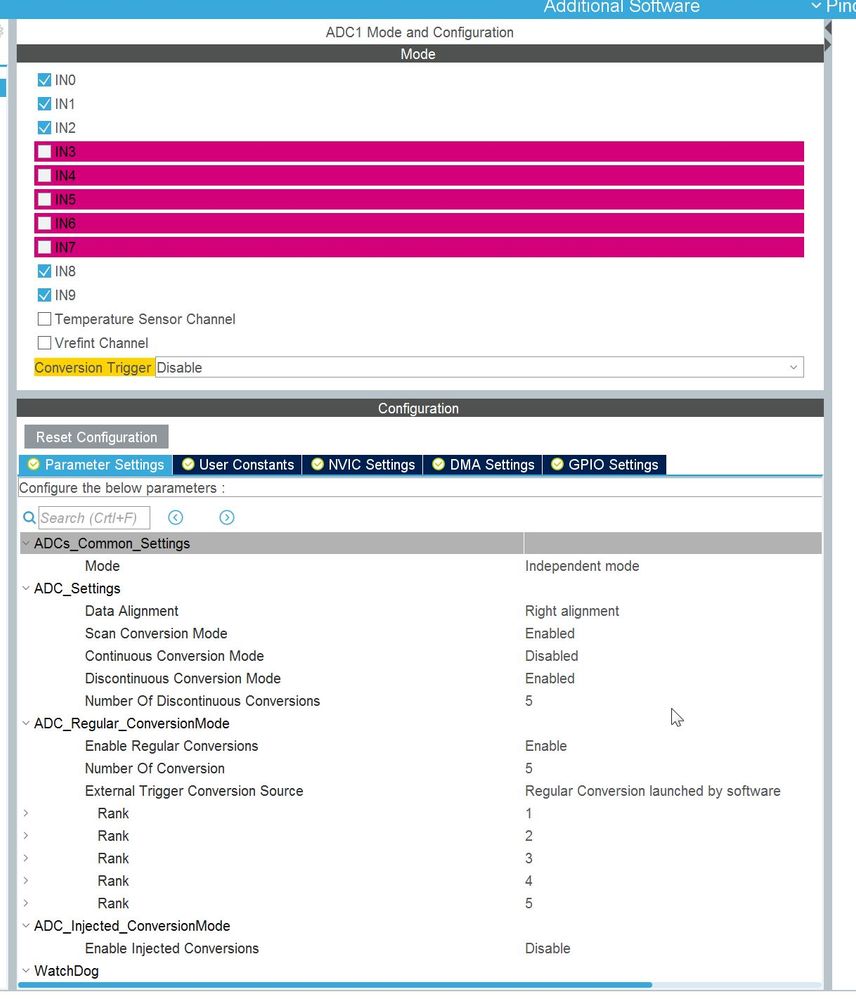

I want to use an ADC with DMA in a STM32F103. I configured it in Cube as you can see in the following picures.

When I start the conversion with

HAL_ADC_Start_DMA(&hadc1,(uint32_t*)AdcData,5);

HAL_ADC_ConvCpltCallback() is called and I see that the AdcData values all changed.

Unfortunately the first rank is sampled twice and the last rank is lost.

I tried to extend the DMA length to 6 but then I do not receive the callback.

I tried to extend the DMA length to 4 but then the last AdcData is unchanged.

Has anybody an idea why this happens and how I can get rid of this?

Solved! Go to Solution.

- Labels:

-

ADC

-

DMA

-

STM32F1 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-04 1:20 PM

Now I found out that the false ADC conversion is triggered by setting the DMA bit when it is already set. Somehow the HAL does not clear this bit at the end of conversion.

I added

hadc1.Instance->CR2 &= ~ADC_CR2_DMA;

to my code after the conversion finished and now it works as expected.

But this is not a good solution.

EDIT:

I now searched for the ADC_CR2_DMA bi in the HAL source file and found

CLEAR_BIT(hadc->Instance->CR2, ADC_CR2_DMA);

only in HAL_ADC_Stop_DMA();

So I have to call HAL_ADC_Stop_DMA() before I can call HAL_ADC_Start_DMA() again?

EDIT:

Nope, calling HAL_ADC_Stop_DMA() causes a DMA_ERROR since the transfer finished already regularly.

Calling HAL_ADC_Init() does not solve this problem either. It does not clear the DMA flag.

So, STM, please review this issue for purpose..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-03 6:19 AM

Read out and check/post the ADC registers content.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-04 1:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-04 1:45 AM

I just found out, that the first sequence is correct (no double data). The second and following sequences are wrong...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-04 3:26 AM

Discontinuous mode is intended to convert a subgroup of the sequence defined in ADC_SQRx. But you set DISCNUM to the same value as ADC_SQR1.L. That doesn't make sense, so just simply don't set DISCEN.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-04 12:41 PM

Hello JW. Thanx for your answer.

Though your answer sounds feasible it doesn't solve my problem.

I set discontinuous mode to "disabled" and regenerated the code.

What I now see is that in the second scan cycle the DMA waits endlessly for data.

I debugged into the HAL and saw, that setting the DMA bit in ADC_CR2 causes the ADC to execute a conversion! This is later the unwanted data..

/* Enable ADC DMA mode */

SET_BIT(hadc->Instance->CR2, ADC_CR2_DMA); // line 1643 of \STM32CubeMX\Drivers\STM32F1xx_HAL_Driver\Src\stm32f1xx_hal_adc.c

Stupid question: What functions should I call to use this ADC in a SW triggered sequence mode?

I do:

- MX_ADC1_Init()

- HAL_ADCEx_Calibration_Start()

- HAL_ADC_Start_DMA()

- HAL_ADC_Start_DMA()

- HAL_ADC_Start_DMA()

- ...

Do I need to reinilialize the ADC between HAL_ADC_Start_DMA()?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-04 1:20 PM

Now I found out that the false ADC conversion is triggered by setting the DMA bit when it is already set. Somehow the HAL does not clear this bit at the end of conversion.

I added

hadc1.Instance->CR2 &= ~ADC_CR2_DMA;

to my code after the conversion finished and now it works as expected.

But this is not a good solution.

EDIT:

I now searched for the ADC_CR2_DMA bi in the HAL source file and found

CLEAR_BIT(hadc->Instance->CR2, ADC_CR2_DMA);

only in HAL_ADC_Stop_DMA();

So I have to call HAL_ADC_Stop_DMA() before I can call HAL_ADC_Start_DMA() again?

EDIT:

Nope, calling HAL_ADC_Stop_DMA() causes a DMA_ERROR since the transfer finished already regularly.

Calling HAL_ADC_Init() does not solve this problem either. It does not clear the DMA flag.

So, STM, please review this issue for purpose..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-05 4:00 AM

> I debugged into the HAL and saw, that setting the DMA bit in ADC_CR2 causes the ADC to execute a conversion!

I don't think so. Why do you think it does?

What's exactly the value written into ADC_CR2?

Does the ADC_SR register indicate a conversion (EOC being set after being 0)?

I don't Cube/HAL, and I personally would write this thing using register access, avoiding confusion stemming from Cube/HAL.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-06 2:22 PM

Hi JW,

why I think setting the DMA bit causes a conversion?

I set a breakpoint to the line where the ADC_CR2_DMA bit is set. Then I reset all registers of the ADC and DMA to the values they had at the first cycle at exactly this location. When I now steped over the code which sets the DMA bit

- the ADC data register content changes,

- the EOC flag goes from 0 to 1

- and the DMA transaction counter decreases..

So I'm quite sure that an ADC conversion is executed when the DMA bit is written by 1 when it already was 1 before.

I will ask a STM supporter to review this..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-08 2:02 PM

Breakpoint stops the processor but not the peripherals, they continue to work. Whether changes in register values during this time are reflected in the displayed values, depend on the toolchain.

>Then I reset all registers of the ADC and DMA to the values they had at the first cycle at exactly this location.

What exactly do you do? Doesn't this start an ADC conversion?

JW

- STM32 and CRA Cyber Resilience Act compliance in STM32 MCUs Security

- STM32F103TBU6 Bare Die / Wafer Availability for R&D Prototyping in STM32 MCUs Products

- STM32H7: jumps in ADC transfer curve; both with Self-calibration, and FactoryLoad in STM32 MCUs Products

- DMA-ADC timed by Tim6 in STM32 MCUs Products

- Stm32f103 samples per second adc in STM32 MCUs Products