- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: ADC Accuracy varies with sample clocks

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ADC Accuracy varies with sample clocks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-11-27 08:39 PM

I am having difficulty getting an equivalent ADC accuracy to my old 8 bit uC with 10 bit ADCs. I am looking to see if anyone can explain why changing the ADC clock cycles affects the ADC accuracy. I would expect longer sampling time would average out any noise. Ultimately I need better accuracy. Would I have better luck going to either STM32F1 with less peripherals, or investigate a different uC altogether? Or is this typical for high speed microcontrollers?

MEASUREMENT DETAILS

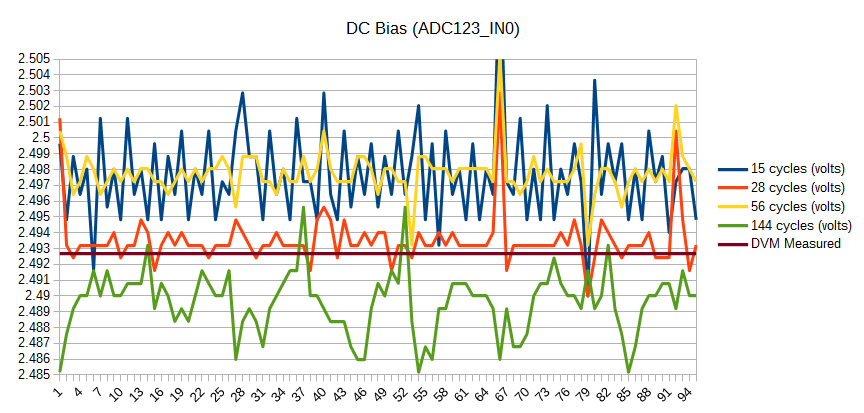

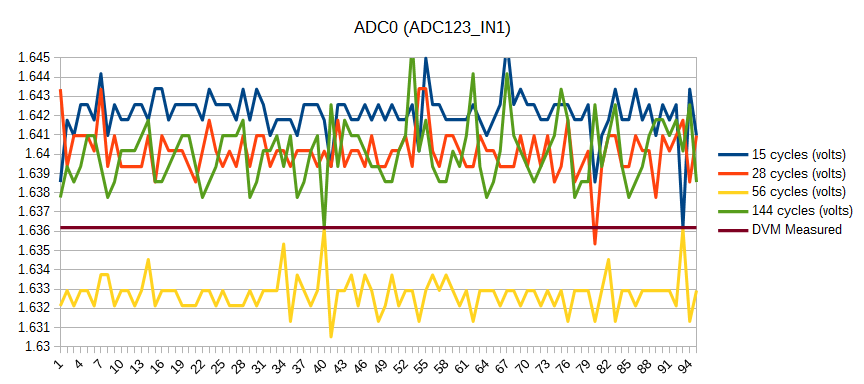

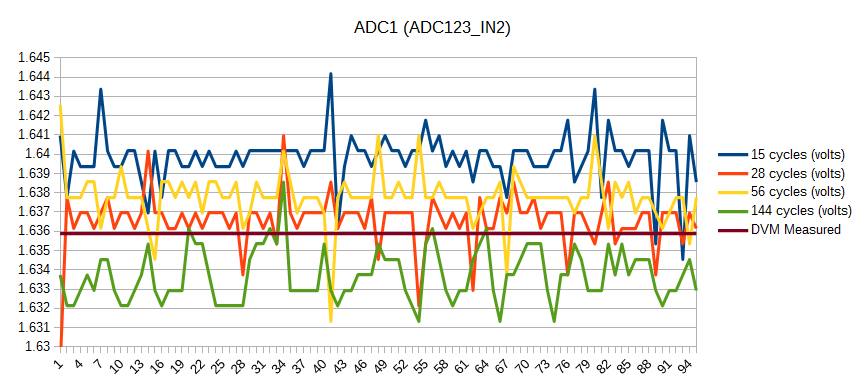

I have 4 different ADC inputs with a constant DC input applied from op amps. ADC scan group was sampled at 76 us. ADC DC voltages where measured with a high res DVM (calibrated) very close to the pads. Vref = 3.2924 which I am using to calculate the converted voltage. I cannot measure any noise on DVM or scope. I did gain some ADC noise improvements by adding some VCC and GND wires close to the pins, but did nothing for accuracy and doesn't explain the strange ADC sample clocks.DATA

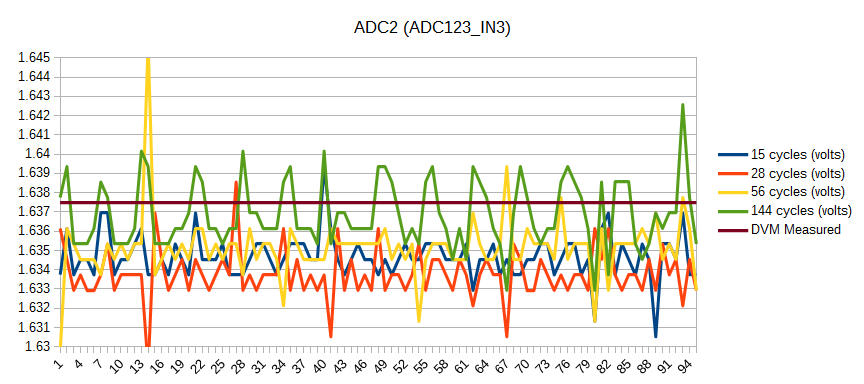

Example 1: ADC123_IN0 This has op amp directly feeding uP ADC. Reference voltage of 2.4927 V. Example 4: ADC123_IN3 Same as above, but different op amp feeding different ADC input.

Example 4: ADC123_IN3 Same as above, but different op amp feeding different ADC input.

I do have a limitation that I'm using a 2 layer board. Bottom side is poured ground around traces. I realize that is difficult to get great ADC results, but that should only affect noise, but does not really explain the accuracy changing with ADC sample time. I did already add a few jumpers which appeared to lower noise but not accuracy.

#adc-accuracy- Labels:

-

ADC

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-25 07:21 AM

You seem to have a periodic noise signal on certain traces. If this is alias of some higher frequency noise, you could easily see 'oddly changing' results.

- sdio not working in STM32 MCUs Products

- LM35 HAL ADC in STM32 MCUs Products

- Nucleo STM32H723ZG ADC 75 MHz or 5MSPS or maximal sample rate in STM32 MCUs Products

- STM32G0B1RE Using a timer to sample a clock signal in STM32 MCUs Products

- External Interrupt is not triggerd in STM32 MCUs Boards and hardware tools