- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: 2019 STM32 Wish List

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

2019 STM32 Wish List

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-31 06:07 AM

Dear Community Members & STM32 fans,

Let’s end 2018 thanking you for your involvement in our Community and wishing you all the best for 2019!

As already done in 2017 (https://community.st.com/s/feed/0D50X00009bLPmvSAG) and in 2018 (https://community.st.com/s/feed/0D50X00009bLSAKSA4), we open this space to hear from you.

This is an opportunity for us to evaluate what we deliver as offer and to know your expectations.

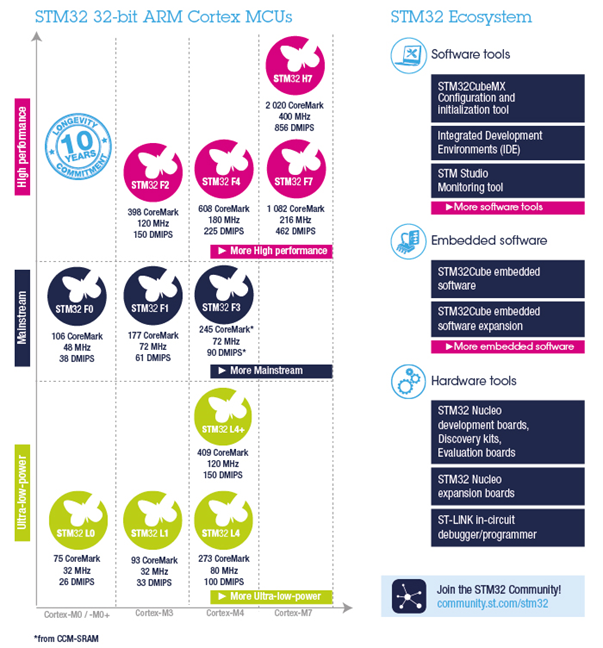

If we come back to the STM32 portfolio end of last year, it was like this:

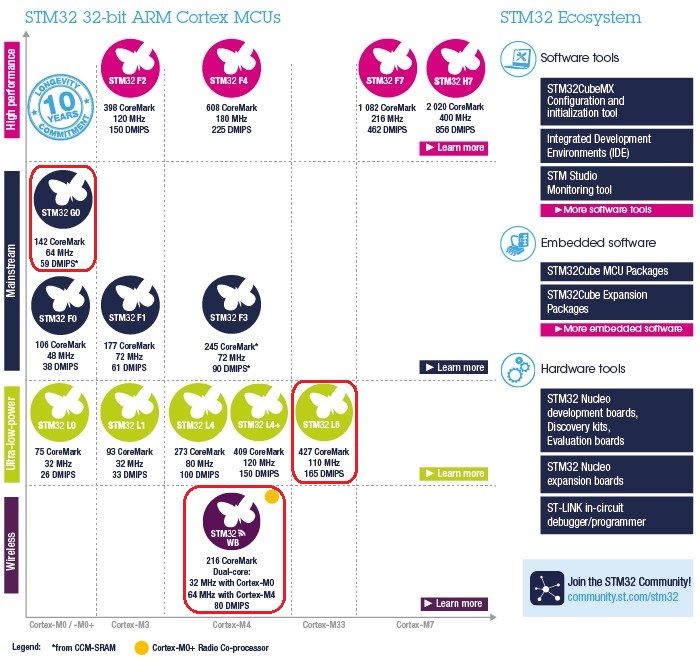

Now the image is getting larger with new products as well as ecosystem components:

Compared to the wishes you shared previous years, we weren’t able to answer all proposals for sure, but may be some of our solutions met what you looked for. Like for example: delivering .ioc file in the STM32Cube package which we started with STM32G0...

Either you are a follower of the STM32 history as well as the Community updates, or a new member in this space, would you mind share with us your feedback answering the following 3 questions:

- What shouldn’t be done (don’t say migration to new Community platform or new CubeMX interface (because both of them will be improved)?

- What you appreciate the most as STM32 related offer?

- What do you expect/suggest related to the STM32 and its ecosystem?

All together, keep UP our STM32 Community!

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-02-09 07:37 AM

Devices:

More powerfull F4/F7/H7 devices in smaller packages (TQFP32,TQFP 44, TQFP48, SO28, SO20, DIP28, DIP40)

More devices with faster (> 6Msps) and beter resolution and precision ADC(16bit) and DAC (16bit)

More analog channels (in and out), more Differental Programmable Gain Amplifier,

More flexible periphery (easier pcb routing )to pin connection with inter connection matrix

Faster SPI with varible speed/data size(bit) and more than CS signal (multidevices on the same spi data bus)

Programmable DDS modul somethink like AD9833 (32 or 48bit accumulator, 12bit/20Mhz or more DAC )

Pecision 24Bit ADC

Simpler and more flaxible (varible data size)DMA channel routing

More advenced Vref module (multi output, varible level )

Hardware debouncing filter for simple mechanical button connection.

Stronger selectable pullup's for I2C pins

Hardware 4x4 keyboard module

Hardware 1wire modul (for chips like DS18b20)

Software:

Faster CubeMx

Built-in calculator for timers

Built-in speed calculator for ADCs and DACs

more examples

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-02-10 05:49 AM

Clive, we've implemented our own version of stlink on an stm32f042 (just over 12k flash). It's fast enough for debugging, but doesn't support swo. It does play well with openocd. With the stm32f042, no crystal is required so it's really a 1-chip solution. We use chibios, so a commercial product would need either to license that or port to another thread package.

Geoffrey

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-02-11 09:24 AM

Crypto-less 'F7x0/'H7x0.

And/or direct sales distributor in Europe, bypassing the US reexport obstacles.

https://community.st.com/s/question/0D50X00009yE4q4SAC/any-chance-for-a-stm32f720

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-02-13 12:18 PM

STM32CubeMX provides easy way to implementing FreeRTOS using two methods;

- Through CMSIS-RTOS abstraction (exisiting)

/* Start thread 1 */

LEDThread1Handle = osThreadCreate(osThread(LED1), NULL);

/* Start scheduler */

osKernelStart();- Through FreeRTOS (generic)

/* Create a task in exactly the same way. */

xTaskCreate( vTask2, ''Task 2'', 240, NULL, 1, NULL );

/* Start the scheduler and executing. */

vTaskStartScheduler();It is a pain for developers familiar with FreeRTOS to have STM32CubeMX force them to use of CMSIS-RTOS API calls. The work around is to manually modify the STMCube generated files to enable use of native FreeRTOS (annoying).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-02-14 02:04 AM

FreeRTOS v10 and FreeRTOS+TCP support in cubeMX

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-02-16 02:37 PM

An M7 (or M4) core in the TSSOP20 or some similar package like the M0s. Sometimes we just need a lot of horsepower in a very small package.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-02-17 06:06 AM

CSP package are the smallest ones around as the package is typically the silicon dice itself.

Only challenge is the selected ball pitch for the chosen CSP...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-02-17 06:11 AM

I don't think the actual core is that large - just put the M7 core, a couple of timers and the I/O Ports, then add a bit of RAM and as much Flash as will fit until you reach the maximum size for the package. NXP used to make such devices with older cores but they also seem to have migrated to a more pins is good strategy.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-02-17 06:15 AM

Avnet Europe don't seem to offer any obstacles but I haven't actually ordered the parts yet. Will be interesting to see what happens.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-02-17 08:06 AM

A Sigma Delta modulator (PDM) hardware block in the L4 series in addition to DAC. Maybe with in interface that looks similar to a DAC interface, and which interpolates between successive values and outputs an SDM bitstream and clock. This would provide better analog performance than PWM and simplify galvanic isolation for bidirectional analog devices such as those doing audio input and output.

- Send sensor data from Nucleo-WL55JC1 and X-NUCLEO-IKS01A2 over LoRaWAN in STM32 MCUs Boards and hardware tools

- C-Library const-correctness in STM32 MCUs Embedded software

- STM32L5: How to integrate STM32TrustZone and TF-M with my project in STM32 MCUs Embedded software

- stm32cubeclt prepending itself to path when vs code is opened in STM32CubeProgrammer (MCUs)

- fail to write on sd card on stm32 g491re in STM32 MCUs Products