Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- STM32L011 Issue w/ LL Comparator Driver

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32L011 Issue w/ LL Comparator Driver

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-24 12:43 PM

Posted on January 24, 2018 at 21:43

Hi All,

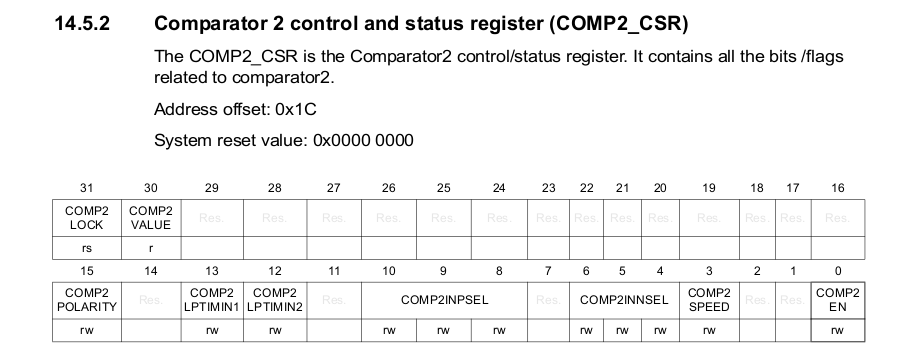

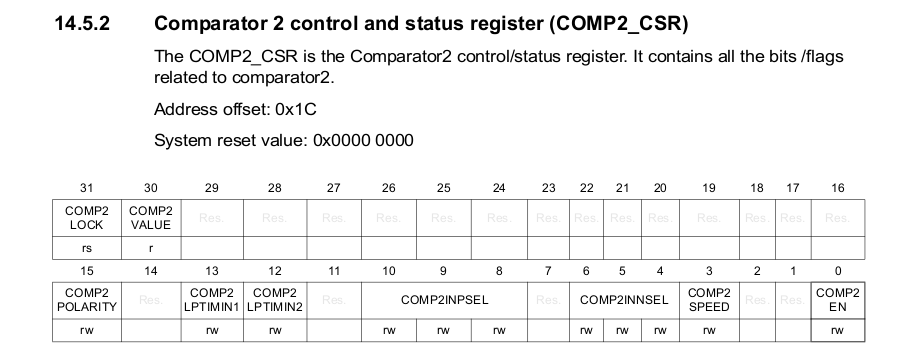

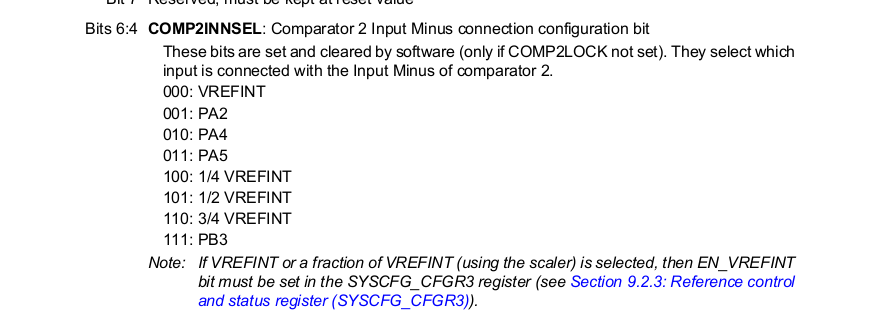

I was having some issues with getting comparator 2 working on my STM32L011K4 (Category 1 Device). I was trying tocompare a voltage on PA7 with 1/2 VREFINT. It wasn't working the way I intended it to. I dug further into the documents and found that the Low Level Drivers (FW_L0_V1.0) provided by ST is missing a bit field that is important to getting comparator 2 working with scalar VREFINT.

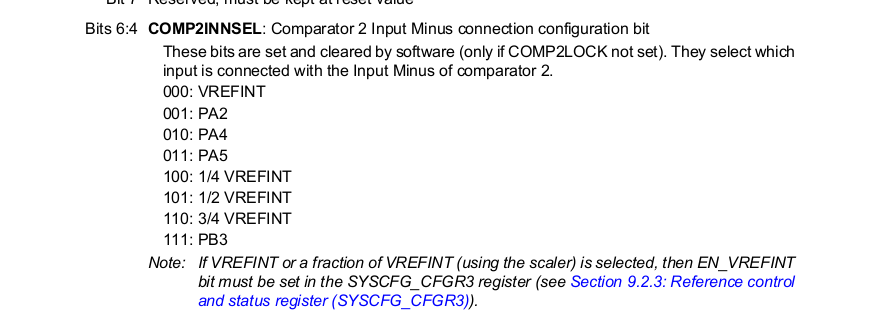

- In order to get scalar VREFINT working on comparator 2, ST states the following:

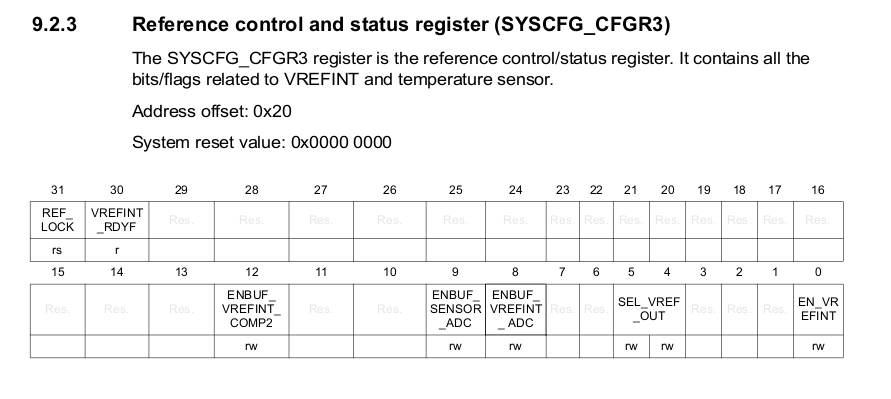

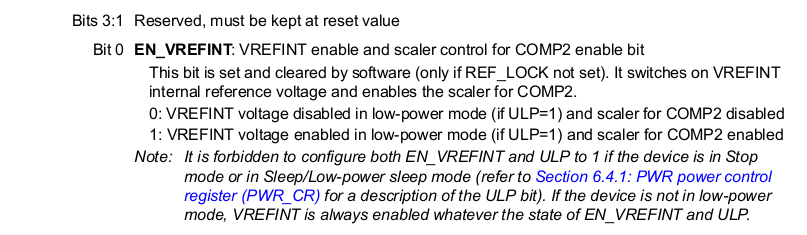

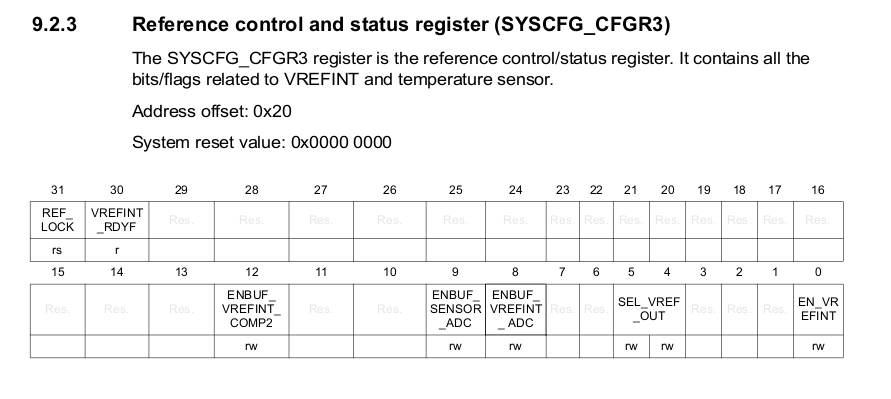

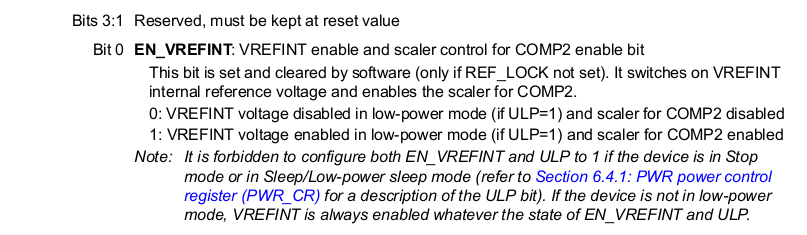

- Moving to SYSCFG_CFGR3, it is clear in the reference manual that you have toset EN_VREFINT to get scalar voltage for COMP2:

- Digging into the drivers stm32l011xx.h, the bit-field EN_VREFINT is missing which in turnstm32l0xx_ll_system.h doesn't have a function to set this bit high:

/***************** Bit definition for SYSCFG_CFGR3 register ****************/

#define SYSCFG_CFGR3_VREF_OUT_Pos (4U)

#define SYSCFG_CFGR3_VREF_OUT_Msk (0x3U << SYSCFG_CFGR3_VREF_OUT_Pos) /*!< 0x00000030 */

#define SYSCFG_CFGR3_VREF_OUT SYSCFG_CFGR3_VREF_OUT_Msk /*!< Verf_ADC connection bit */

#define SYSCFG_CFGR3_VREF_OUT_0 (0x1U << SYSCFG_CFGR3_VREF_OUT_Pos) /*!< 0x00000010 */

#define SYSCFG_CFGR3_VREF_OUT_1 (0x2U << SYSCFG_CFGR3_VREF_OUT_Pos) /*!< 0x00000020 */

#define SYSCFG_CFGR3_ENBUF_VREFINT_ADC_Pos (8U)

#define SYSCFG_CFGR3_ENBUF_VREFINT_ADC_Msk (0x1U << SYSCFG_CFGR3_ENBUF_VREFINT_ADC_Pos) /*!< 0x00000100 */

#define SYSCFG_CFGR3_ENBUF_VREFINT_ADC SYSCFG_CFGR3_ENBUF_VREFINT_ADC_Msk /*!< VREFINT reference for ADC enable bit */

#define SYSCFG_CFGR3_ENBUF_SENSOR_ADC_Pos (9U)

#define SYSCFG_CFGR3_ENBUF_SENSOR_ADC_Msk (0x1U << SYSCFG_CFGR3_ENBUF_SENSOR_ADC_Pos) /*!< 0x00000200 */

#define SYSCFG_CFGR3_ENBUF_SENSOR_ADC SYSCFG_CFGR3_ENBUF_SENSOR_ADC_Msk /*!< Sensor reference for ADC enable bit */

#define SYSCFG_CFGR3_ENBUFLP_VREFINT_COMP_Pos (12U)

#define SYSCFG_CFGR3_ENBUFLP_VREFINT_COMP_Msk (0x1U << SYSCFG_CFGR3_ENBUFLP_VREFINT_COMP_Pos) /*!< 0x00001000 */

#define SYSCFG_CFGR3_ENBUFLP_VREFINT_COMP SYSCFG_CFGR3_ENBUFLP_VREFINT_COMP_Msk /*!< VREFINT reference for comparator 2 enable bit */

#define SYSCFG_CFGR3_VREFINT_RDYF_Pos (30U)

#define SYSCFG_CFGR3_VREFINT_RDYF_Msk (0x1U << SYSCFG_CFGR3_VREFINT_RDYF_Pos) /*!< 0x40000000 */

#define SYSCFG_CFGR3_VREFINT_RDYF SYSCFG_CFGR3_VREFINT_RDYF_Msk /*!< VREFINT ready flag */

#define SYSCFG_CFGR3_REF_LOCK_Pos (31U)

#define SYSCFG_CFGR3_REF_LOCK_Msk (0x1U << SYSCFG_CFGR3_REF_LOCK_Pos) /*!< 0x80000000 */

#define SYSCFG_CFGR3_REF_LOCK SYSCFG_CFGR3_REF_LOCK_Msk /*!< CFGR3 lock bit */

/* Legacy defines */

#define SYSCFG_CFGR3_ENBUF_BGAP_ADC SYSCFG_CFGR3_ENBUF_VREFINT_ADC

#define SYSCFG_CFGR3_ENBUFLP_BGAP_COMP SYSCFG_CFGR3_ENBUFLP_VREFINT_COMP

#define SYSCFG_VREFINT_ADC_RDYF SYSCFG_CFGR3_VREFINT_RDYF

#define SYSCFG_CFGR3_SENSOR_ADC_RDYF SYSCFG_CFGR3_VREFINT_RDYF

#define SYSCFG_CFGR3_VREFINT_ADC_RDYF SYSCFG_CFGR3_VREFINT_RDYF

#define SYSCFG_CFGR3_VREFINT_COMP_RDYF SYSCFG_CFGR3_VREFINT_RDYF�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?- My current workaround for testing purpose is to modify a function in stm32l0xx_ll_system.h:

/**

* @brief Buffer used to generate VREFINT reference for comparator enable

* @rmtoll SYSCFG_CFGR3 ENBUF_VREFINT_COMP LL_SYSCFG_VREFINT_EnableCOMP

* @retval None

*/

__STATIC_INLINE void LL_SYSCFG_VREFINT_EnableCOMP(void)

{

SET_BIT(SYSCFG->CFGR3, SYSCFG_CFGR3_ENBUFLP_VREFINT_COMP);

SET_BIT(SYSCFG->CFGR3, 0x1); // Setting EN_VREFINT to '1'

}

�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?This workaround seems to have worked for me. I hope this is the issue and if so, gets fixed on the next version of the firmware.

Thanks!

#driver-issue #ll-drivers

Labels:

- Labels:

-

STM32Cube MCU Packages

-

STM32L0 Series

0 REPLIES 0

Related Content

- STM32U5A5ZJ comparator interrupts in STM32 MCUs Embedded software

- Sensorless BLDC Motor control using an external comparator and interrupt. in STM32 MCUs Motor control

- STM32L433RC Comparator interrupt triggering on both edges rather than just rising edge. in STM32 MCUs Products

- STM32L011f3p6 using UART RECEIVE IT mode with HAL. in STM32 MCUs Embedded software

- Why is the B-G431B-ESC1 board using L6387E as gate driver? (incompatible logic level) in STM32 MCUs Motor control