- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Re: STM32F37x, USB, Endpoints and their toggle bit...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F37x, USB, Endpoints and their toggle bits

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-03-26 01:04 AM

I'm not alone in my confusion I think, when taking in the information of RM0313, rev6, page 838. And that is how to handle the 't' (toggle bits) in the EP registers.

Where RM0313 mentions that read-modify-write is be avoided, I see in ST's code (and others), through the many perverse #define(s), that that very thing happens.

Could the take on this be that an r-m-w cycle is necessary, but care must be taken to adjust the temporary variable (used on the read) to clear those 't ' bits not involved (so they won't be toggled), before writing the variable back?

Further, about set/clr of involved 't' bit(s). To set a 't' bit is must be at the cleared state, conversely, to clear a 't ' bit it must be at the set state.

And may I take this opportunity to mention RM0313 rev 6, sec 29.6.2, page 843. The text has the word 'address' which I feel sure is not reflective. It should be 'offset'

Workalot

- Labels:

-

STM32F3 Series

-

USB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-04-06 07:15 AM

> It may be that most of the real-world applications operate endpoints in such pairs,

Alas, CDC does no follow that model. Well, kinda. It requires an in/out pair for that actual "serial port" data, and a 2nd "in" endpoint for modem status. I ran in to this trying to implement "as many CDCs as possible" and wound up with 3 on a G4. I was hoping for more given the ref man mentions "up to 16 mono-directional endpoints". Yes, there are 16 mono-directional EPs, but 8 of them are hard-wired as IN and 8 are hard wired for OUT. The F4 would only support 2 (I think - it has been a while since that project).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-04-15 12:04 AM

Got there, finally! I have a working CDC VCP. Must mention JW's...

>However, the device-only USB in STM32 is a somewhat lower-level implementation, where STATUS phase of handhsake is to be performed "manually".

... that bit of information puzzled me initially, how does one determine when and where does the Status Stage appear/occur. Nevertheless, thoughts come into focus, trials and tribulations exercised, and et voila!

Workalot is happy to share his results - I can post the module if there is interest.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-04-17 04:47 AM

"He programmed, he debugged, and did it again

Advances were slow yet he strived to maintain

A learned STM32 soul would see as watcher

That Workalot's fate was sealed by a gotcha."

Had hoped the STM32F37x could be part of a set of MCUs I implement for control applications.

Its all to do with the placement in memory of the GPIO module. JW elsewhere made this clear.

Workalot

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-04-17 11:53 AM

What's the issue?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-04-17 03:14 PM

I have a question how could CTR_RX and CTR_TX co-exist? Is not USB a half-duplex data I/O stream? That is, request/response in a lockstep arrangement.:thumbs_up::thumbs_up:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-04-17 03:26 PM

I implement bit-banding in my digital I/O application. The STM32F37x's GPIO module is located at 0x48000000, well outside of the 1MB bit-banding space.

While the F37x manual confirms that bit-banding is supported, it didn't go as far to mention the GPIO isn't. And of course, I didn't go looking - that is the gotcha.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-04-17 11:14 PM

> Is not USB a half-duplex data I/O stream?

As I've said above:

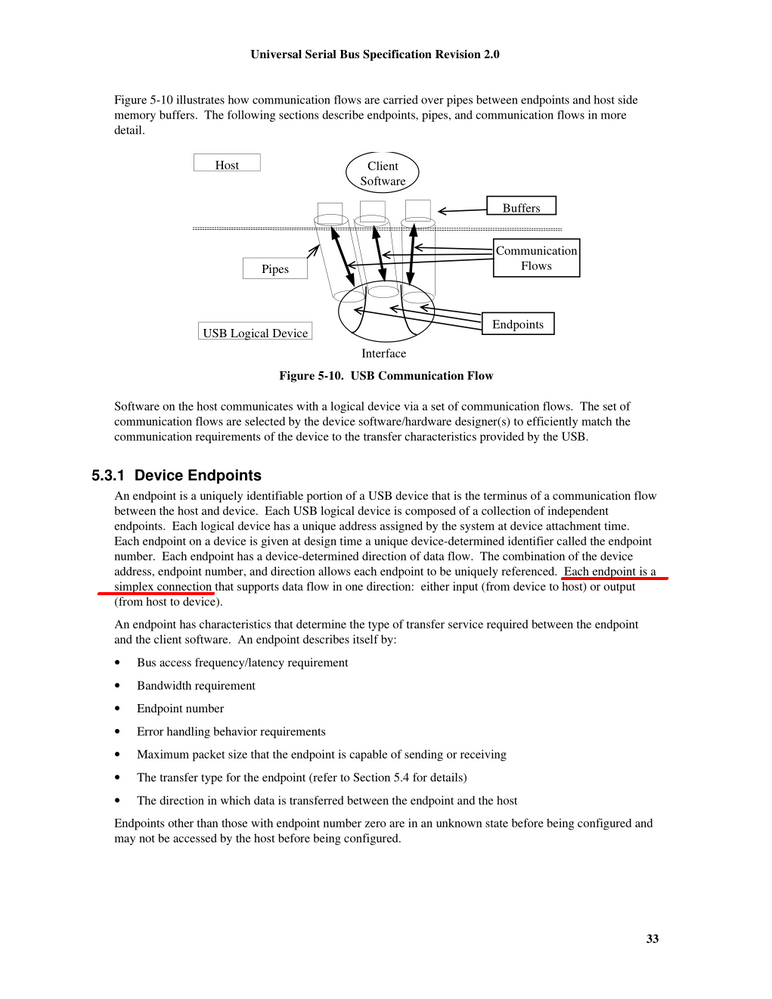

> No. Endpoints are simplex and mutually independent. Or, from the horse's mouth:

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-04-17 11:17 PM

Oh I see. Yes, a gotcha indeed.

You are probably aware of the GPIO_BSRR register which provides (through a mechanism different to bitbanding and local to the GPIO module) a perfect atomic write to individual output bits in GPIO_ODR. It does not provide individual-bit-addressability nor atomic access to other GPIO registers, though.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-04-18 01:42 AM

Yes, indeed I am aware of BSRR. STM, Atmel (Microchip) and others do the atomic write only thing as a matter of course.

And on your 'lockstep' comment: I had my UART mindset about when I posed the question. A very thing that Jan Axelson makes advice on.

While the result failed to please, the journey was pleasant. Mostly from JW's edification, thank you for taking the time.

Workalot

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-05-25 01:53 AM

JS

Not sure what you are referring to. If it is about the STM32F37x's USB peripheral and its endpoint representation in silicon I can say that I have my USB/VCP coded to use EP1 as interrupt IN and EP2 for Rx/Tx.

I did mention how other code I have reviewed implement EP2 as an Tx and EP3 as an Rx (maybe it was vice versa) which I suggest was all to do with avoiding Tx interrupt handling when within the Rx handler.

But on another note, a ta da!

Workalot's previous grief on a gotcha has proven to be premature, all wasn't as bad as it seemed. Taking a break from the project had me realize (when I was about 400km away) that the lack of bit-banding of the GPIO can be handled through IDR and BSRR (JW) accesses.

So the STM32F37x is now happily included in a small family of demo platforms.

Must say, weight for age the STM32F37x is a likeable MCU.

- « Previous

-

- 1

- 2

- Next »