- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Re: STM32F101 with StdPeriph_Lib

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F101 with StdPeriph_Lib

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-15 11:12 PM

Hi,

I'm working on a new project, 2 boards: STM32F101CBT6 and STM32F101T6U6ATR.

I've generated a project/code via Cube (which has many advantages), but, similar to other posts - the HAL layer is, simply, lot's of code which make things complex, but not HAL-able.

The old StdPeriph_Lib was not bad, I've used it a few times successfully.

I downloaded stm32F10x_StdPeriph_Lib_V3.5.0, but it's from 2011 - is there anything more up-to-date?

I adapted the project to my STM32F101T6U6ATR (32K flash, 6K RAM, 36Mhz), and added minimal code for a 1ms SisTick and a GPIO, which toggles every second (a simple test I do, reading with an analyzer, to test the clock) - but my 1 second is about 9 seconds!!!

What am I missing?

Thanks

#stm32-stdperiph_lib #stm32f101- Labels:

-

SPL

-

STM32F1 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-15 11:45 PM

Hi

Rosenbaum.Rami

,The last STM32F1 SPL library version is the one available on the web (

).The maintenance priority is given for the Cube package.

But asyou are not convinced to use it (I am curious to know if you faced any particular issue using the Cube package), I recommend you review the clock settings of your application.

There are 2 examples in the SPL that you may take as reference:

- STM32F10x_StdPeriph_Lib_V3.5.0\Project\STM32F10x_StdPeriph_Examples\SysTick\TimeBase: '

This example shows how to configure the SysTick to generate a time base equal to1 ms. The system clock is set to 24 MHz on Value line devices and to 72 MHz on other devices, the SysTick is clocked by the AHB clock (HCLK).

' - STM32F10x_StdPeriph_Lib_V3.5.0\Project\STM32F10x_StdPeriph_Examples\GPIO\IOToggle

-Amel

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-16 2:02 AM

... - but my 1 second is about 9 seconds!!!

What am I missing?

Perhaps that obvious design bug in the SPL header files.

Check the value of the define '

HSE_VALUE

' in your project. If you give none, it is silently set to 8.000.000 (or 25.000.000 for the CL parts) in the headerstm32f10x.h

, instead of throwing an error.This usually makes your clock setting fail, and fall back to the default HSI clock.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-16 2:52 AM

I did use both for reference.

Toggling a GPIO works.

Receiving SysTick interrupts work.

Only the timing is terrible.

The STM32F101 family work on 36MHz and the board I'm currently testing has no external clock.

It's not a value line, so I use the STM32F10X_LD define.

My '1000ms' toggle turns out as 4.486 seconds.

4.486 * 8MHz ~= 36MHz.

HCLK_Frequency

is 8,000,000, when calling:RCC_GetClocksFreq(&RCC_ClockFreq);

even though

SystemCoreClock

is 36,000,000.I must admit that configuring all these clocks/plls is new to me.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-16 3:09 AM

... even though

SystemCoreClock

is 36,000,000.Read the comments to the

SystemCoreClockUpdate()

function in system_stm32f10x.h. The (initial) value of theSystemCoreClock

variable is not necessarily correct. Or rather, it is initially incorrect, since it is initialized to the target clock frequency before the functionSystemInit()

is called.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-16 3:12 AM

Hi,

In this board I don't have an HSE - I'm supposed to use the HSI.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-16 3:19 AM

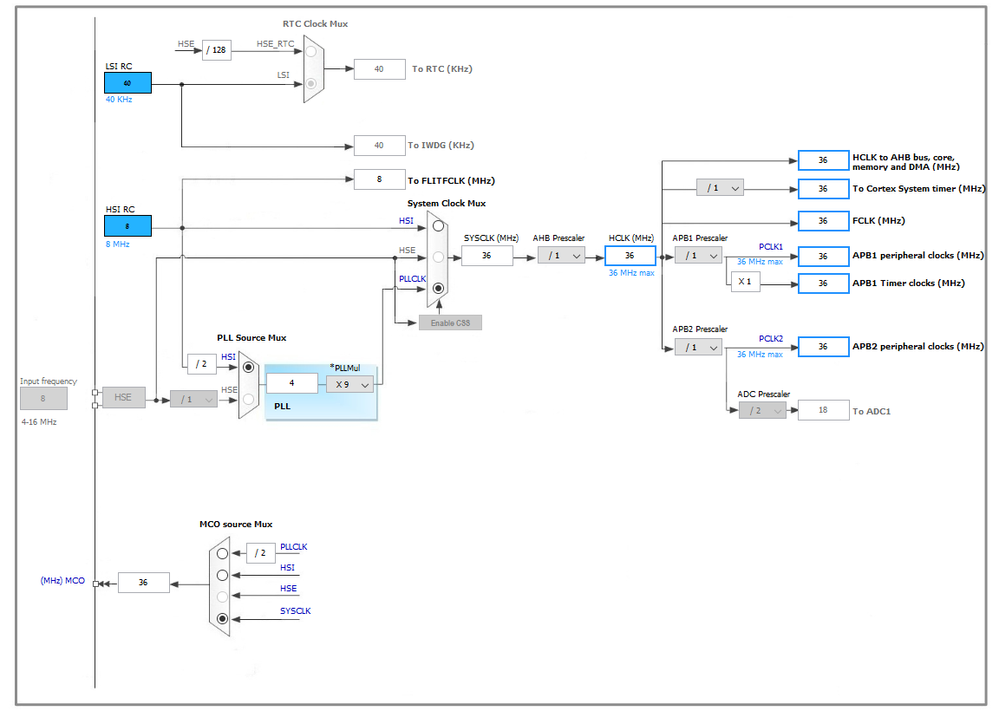

This is the clock configuration that works fine, created by the CubeMX.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-16 4:20 AM

That is o.k., but you need to check if the files

system_stm32f10x.c

andsystem_stm32f10x.h

match your purpose. They had usually been generated by an Excel Sheet (perhaps still found somewhere on the ST downloads) for a specific configuration. The SPL examples mostly use the same configuration (HSE, max. core clock), which is not what you want then.I suggest to step through the system init code with a debugger (or just read it), and see what it actually does and what changes you would need to make.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-16 4:26 AM

I agree... bummer... hoped someone has done it already

thanks

- STM32Cube Does Not Work After Formatting the Computer in STM32CubeIDE (MCUs)

- Code Debugging using STLINKV2 in STM32 MCUs Boards and hardware tools

- One-time HID bootloader? ("destroying" the STM32F103's ability to load bootloader again) ? in STM32 MCUs Products

- Error: Failed to erase memory on (Bluepill) STM32F103C8T6 in STM32CubeProgrammer (MCUs)

- stm32f103vet6 no osc no cap Swd download ok in STM32 MCUs Products