- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Re: Issues while writing into an External NOR whil...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Issues while writing into an External NOR while XiP from a different section of same External NOR

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-01 10:11 AM - edited 2023-09-01 10:13 AM

Hello,

I am working on a custom PCB with STM32H753 microcontroller and an External NOR flash memory to which I am accessing via FMC interface @ 0x60000000.

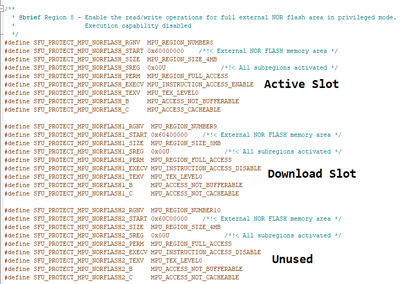

I have a secure boot (SBSFU) running on the internal flash of the uC and my application executes on the External NOR flash to which I am jumping to from the secure boot. My architecture is to use a section of the External NOR flash (Top 4MB) for execution of my application (Active slot) and another section of the same NOR flash (next 4MB) as a storage space for some raw binary data (Download slot).

If I use a programmer like ST-Link V2 and write to the Download slot through a tool such as STM32CubeProgrammer, the Secure boot detects it and swaps it to the active slot, thereby executing it subsequently.

My problem is this:

I am trying to use my running application in the active slot to receive binary from outside (via Ethernet) and write to the Download slot by using HAL NOR program function. Here, I am facing some random behaviour where the data seems to write to the Download slot address (as seen in the Memory tab during debugging in STM32CubeIDE) but the data is not retained in memory on a power-off reset.

On some research, I figured out that the data cache was holding the data and not writing to the External NOR Flash memory due to the non-support for hardware coherency in STM32H7 as per AN4838. But, when I disable the Data cache alone in my application, I see that the NOR flash memory is being written with a small amount of data and the data is also retained on a power-off reset. So, it looks like this is a working possibility, but I am not able to figure out the right configurations that I need to have in my environment to have this working on a repetitive basis. I have enabled the Memory Protection Unit (MPU) on my secure boot and have defined the NOR flash memory region, also partitioned it and tried out the different settings as mentioned in AN4838, but to no avail.

Can someone please help me with this?

Thanks and regards,

Sreedhar

- Labels:

-

STM32Cube MCU Packages

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-01 10:22 AM

The NOR Flash is unlikely to be able support concurrent execution and writing. You'd need to update content whilst running from internal Flash, and you'd want a non-cached, in-order, interaction with the NOR across it's entire addressable space.

You don't mention a specific device, but I'd expect the unlock / magic sequences aren't well bounded.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-03 09:12 PM

Hello @Tesla DeLorean ,

Thanks a lot for your insight. I was of the same insight for a while, until I managed to make the write happen using a small light-weight project while executing concurrently from a different part of the same memory. That is somehow pushing me to get this to work with a bigger application.

I am using this part for the External NOR Flash FYI - MT28EW256ABA1LPC-0SIT

https://in.micron.com/products/nor-flash/parallel-nor-flash/part-catalog/mt28ew256aba1lpc-0sit

Does it give any hints?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 06:58 AM

This flash supports read while writing or erasing in another sector. See the very first page of the datasheet. Not sure how this works with XIP... it should, without any caching or "speculative execution" anomalies.

- Nested interrupts on the Nucleo-F411RE in STM32 MCUs Products

- What parameters to use for the external MX661G45... Flash on the STM32H7S78-DK in STM32 MCUs Products

- STM32F722ZE: ST- Link cut off, how do I write the STM32 target board in STM32 MCUs Boards and hardware tools

- Struggling with HSE in STM32CubeMX (MCUs)

- How to manage using external flash in command mode while simultaneously running firmware from it in memory mapped mode? in STM32 MCUs Embedded software