- STMicroelectronics Community

- MEMS and sensors

- MEMS (sensors)

- Re: I'm using the LIS3DH. Do I need to provide a 9...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I'm using the LIS3DH. Do I need to provide a 90 mS delay between configuration of CTRL_REG1 and reading the OUT registers or the FIFO to insure stable output ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-10 04:41 PM

I'm using the LIS3DH. The Application Note AN3308 specifies a 90 mS delay time between configuration and reading data in the suggested procedure for performing a self test, (p57 of DocID18198 Rev 3). The delay is, "... for stable output". Once ODR is set or FIFO enabled, is a delay required to insure stable data? If so, how long of a delay is adequate? 90 mS eats up a lot of power while the LIS3DH is just sitting there. Would 5 mS or 0 mS be OK?

Solved! Go to Solution.

- Labels:

-

Accelerometers

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-11 01:10 AM

Hi @JMatt ,

This 90ms delay refer to the Self Test condition only, which is sensible to small variation since the actuation force applied to the sensor (simulating a definite input acceleration) is huge.

It is not necessary to wait such delay for a standard acquisition (continuous or FIFO mode).

Of course, you'll need 1/ODR to get a valid data after internal digital conversion. Moreover, it is a general recommendation to discard the first sample coming just after the register configuration.

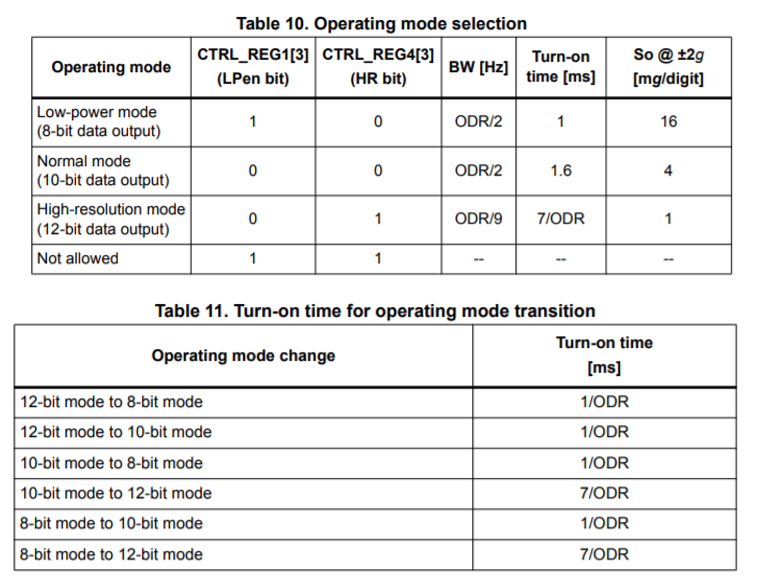

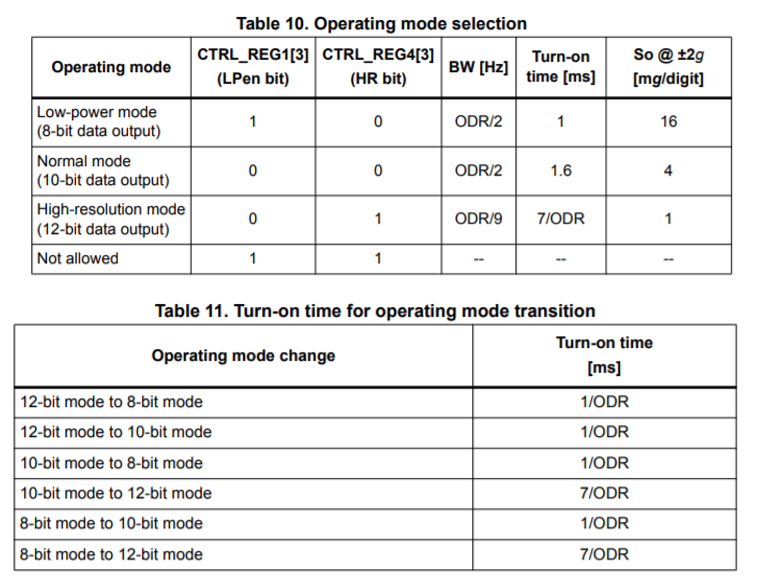

For a general overview on the power-on timings, I suggest you to check the datasheet p.16 and 17 (following tables):

-Eleon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-11 01:10 AM

Hi @JMatt ,

This 90ms delay refer to the Self Test condition only, which is sensible to small variation since the actuation force applied to the sensor (simulating a definite input acceleration) is huge.

It is not necessary to wait such delay for a standard acquisition (continuous or FIFO mode).

Of course, you'll need 1/ODR to get a valid data after internal digital conversion. Moreover, it is a general recommendation to discard the first sample coming just after the register configuration.

For a general overview on the power-on timings, I suggest you to check the datasheet p.16 and 17 (following tables):

-Eleon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-11 05:02 AM

Thank you.

- LIS2DE12 coherency in bypass mode in MEMS (sensors)

- LPS28DFW one shot bit cleared before sample is ready? in MEMS (sensors)

- IIS3DWB: Issues with RMS Accuracy Using IIS3DWB on Z-Axis at Higher Frequencies in MEMS (sensors)

- ISM330DLC fifo settings issue in MEMS (sensors)

- Get IIS2DH data with data ready interrupt in MEMS (sensors)