- STMicroelectronics Community

- MEMS and sensors

- MEMS (sensors)

- Re: CS behavior for LPS22HH

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

CS behavior for LPS22HH

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-14 8:13 AM

Hello,

We are using LPS22HH in SPI mode in our project.

It seems that tying nCS =0 (not toggling it) disables SPI communication altogether.

Is this observation correct?

Does the nCS signal need to be toggled (asserted-deasserted) in order to trigger some internal state machine that enables communication?

Thanks

Solved! Go to Solution.

- Labels:

-

Environmental Sensors

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-14 11:40 PM

Hi @Community member ,

please note that your "Scenario n.1" is very similar to "Scenario n.2" in most cases, since a floating pad voltage value is often close to 0V, mostly depending on the surrounding electrical environment.

The third scenario, i.e. nCS pad transition from Vdd to GND, followed by the clock activation, is the requested one. This is valid in general for the SPI communication, and explicitly for ST sensors, since it is the trigger for the ASIC internal SPI state machine, as suggested by yourself.

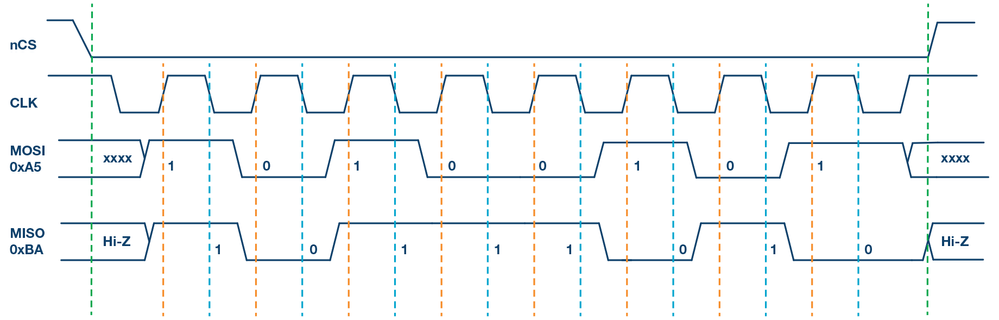

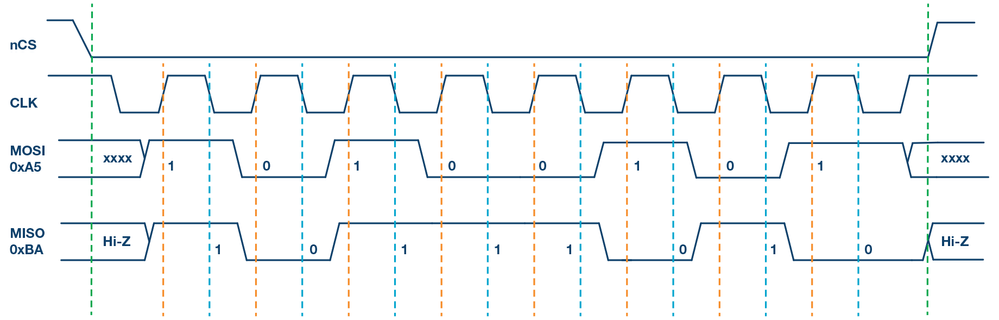

Please note that usually ST sensors run in SPI Mode 3, as depicted here below:

-Eleon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-14 8:34 AM

Hi @Community member ,

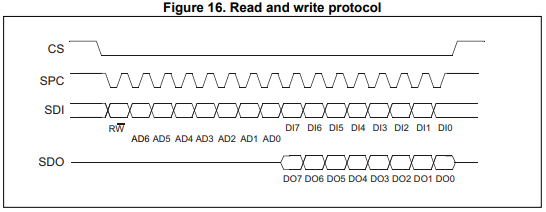

the SPI communication starts after transition high to low of the CS pin, as you can see in the datasheet, p 29.

-Eleon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-14 8:44 AM

Hi @Eleon BORLINI , thanks for your prompt response.

We have tested 2 scenarios:

- nCS asserted (=0) at all times - communication failed

- nCS floats (hi-Z) when deasserted and 0 when asserted - still no communication

I guess that a 3rd scenario works as depicted in the datasheet but my question is whether scenario 1 should/can work as well (as we have some hardware constarints) ??

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-14 11:40 PM

Hi @Community member ,

please note that your "Scenario n.1" is very similar to "Scenario n.2" in most cases, since a floating pad voltage value is often close to 0V, mostly depending on the surrounding electrical environment.

The third scenario, i.e. nCS pad transition from Vdd to GND, followed by the clock activation, is the requested one. This is valid in general for the SPI communication, and explicitly for ST sensors, since it is the trigger for the ASIC internal SPI state machine, as suggested by yourself.

Please note that usually ST sensors run in SPI Mode 3, as depicted here below:

-Eleon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-22 4:42 AM

Hi @Community member ,

were you able to test the "3rd scenario" (nCS toggled), or do you ave hardware constrains at app level?

-Eleon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-22 2:18 PM

Hi @Eleon BORLINI

We did (though had to rework the hardware) and it works.

Thanks

- LIS3DH Module: Unexpected Power Consumption in Power-Down and Low-Power modes in MEMS (sensors)

- Unexpected Double Interrupt on LSM6DSV16X FIFO Watermark Event in MEMS (sensors)

- Issue with Wrist Tilt Direction Detection on LSM6DS3TR-C in MEMS (sensors)

- Problems with initialization of VL53L1X in Imaging (sensors)

- Mems studio fsm debug in MEMS (sensors)