- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32F30x count external pulse Up/Down

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F30x count external pulse Up/Down

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-06 05:40 AM

Hi

,I would like to

know

if is possible set

a timer

or other peripheral on the STM32F30x

to count

up or down

the pulses applied

to a pin

depending on the

logic level

applied

to a second

input

. For example if the second input is high the pulse are counted Up instead if the second input is low the pulse are counted Down.I have carefully read

the

timersection on the

reference manual

but have not found

how to set

the timer

to achieve this functionality

.Please let me know. Thank you.

#stm32f30x- Labels:

-

STM32F3 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-06 06:04 AM

Hi

OK. Configure the timer as a counter, clocked by the external input, the IP to be counted. The second input, using IRQ so needs to be a EXTI IO. The IRQ should edge triggered (will have to look up to see if this is possible). On IRQ, the ISR checks the level and changes the timer count direction.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-06 06:47 AM

Thanks

for your suggestion

but

a software solution

is too

slow

. Untilthe

ISR

is completed

the incoming pulses

are counted

in the wrong direction

.I

'm looking for ahardware solution

.Thanks anyway

.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-06 07:53 AM

''

but

a software solution

is too

slow

. Untilthe

ISR

is completed

the incoming pulses

are counted

in the wrong direction

.I

'm looking for ahardware solution

. '' What kind of pulse rate/frequency are we talking about? The ISR can complete in a few micro seconds, possible down to nano seconds with the right device (clocking at 168MHz) and a bit of hand coding the ISR.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-06 09:17 AM

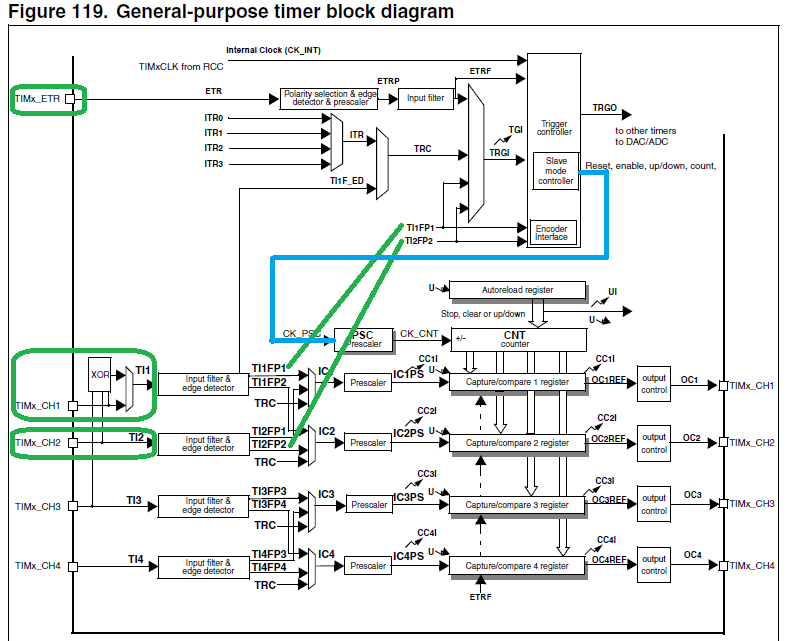

Encoder mode, TIM2 example, end of thread

[DEAD LINK /public/STe2ecommunities/mcu/Lists/STM32Discovery/Flat.aspx?RootFolder=/public/STe2ecommunities/mcu/Lists/STM32Discovery/STM32F3%20Discovery%20Counter&FolderCTID=0x01200200770978C69A1141439FE559EB459D75800084C20D8867EAD444A5987D47BE638E0F&TopicsView=https://my.st.com/public/STe2ecommunities/mcu/Lists/STM32Discovery/AllItems.aspx¤tviews=94]https://my.st.com/public/STe2ecommunities/mcu/Lists/STM32Discovery/Flat.aspx?RootFolder=/public/STe2ecommunities/mcu/Lists/STM32Discovery/STM32F3%20Discovery%20Counter&FolderCTID=0x01200200770978C69A1141439FE559EB459D75800084C20D8867EAD444A5987D47BE638E0F&TopicsView=https://my.st.com/public/STe2ecommunities/mcu/Lists/STM32Discovery/AllItems.aspx¤tviews=94Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-07 05:30 AM

T

he problem is not

the frequency

of the pulses

but the time

between

the change

of input

that defines the

count direction (up or down

)and the next

clock edge

.In my case

this

time

can be up to

1us

.Consider

also

that

other

ISR

triggered

at the same time

can

further increase

the response time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-07 05:43 AM

Clive1 many thanks for your suggestion but as per reference manual (page 480) in

TIM_EncoderMode_TI1- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-07 06:45 AM

The Up/Down on one signal versus the clock edge of the other sounds exactly like

http://www.edn.com/design/integrated-circuit-design/4363949/Decode-a-quadrature-encoder-in-software

. I haven't looked at the F3 docs thoroughly, but the F4 suggests it can clock on the edge of one signal, instead of the edges of both, if configured correctly, and you can pick which. To understand relative phase, then perhaps input capture of both edges, in different channels, and then interrupting on the trailing one, and either measuring the periodicity or phase relationship based on current and prior values.Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-21 08:21 AM

Dear Clive1,

thanks for your suggestion. I have try the code that you link in the previous post and I have found the following problem: 1) The RM0316 documentation regarding SMS slave Mode Selection say: ''0001: Encoder mode 1 - Counter counts up/down on TI2FP2 edge depending on TI1FP1 level.''. Instead I found the counter change on the TI1FP1 edge and not TI2FP2. 2) If the clock input is low after timer initialization the counter count down on the falling edge instead if the clock input is high after timer initialization the counter count up on the rising edge of the clock input. Please note that this happen with the second (direction) signal stable. I think the point 1 is a simple typo error but the point 2 behavior is a big problem because after power on I need to be sure about the count direction and active edge regardless to the clock signal level at power on. Any idea? There is somewhere a detailed view of the Slave Mode Conrtoller to better understand the logic? Thanks.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-21 09:02 AM

#1 Yes RM0090 is like that too, the library code defines it the other way around, which I think is correct.

#2 I'm not sure what you're going to do about initial conditions, if the external states don't match the internal ones there will be a perceived edge/transition. You can swap the pin designations in hardware or software. The signal is not directly connected to the pin, it goes through a synchronizer and a filter/edge detector.

Up vote any posts that you find helpful, it shows what's working..

- Clarification on how to route FMC and LCD RGB traces of STM32F7 series MCU in STM32 MCUs Products

- SPI with DMA is not working in stm32g0 in STM32 MCUs Products

- Missing case for ADC2 software start in STM32f7xx HAL driver HAL_Adc_Start_IT() in STM32 MCUs Embedded software

- RTC Oscillator not stable in STM32 MCUs Products

- No texts appear on the LCD with TouchGFX in STM32 MCUs TouchGFX and GUI