- STMicroelectronics Community

- Product forums

- STM8 MCUs

- stm8s cco flag never set

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

stm8s cco flag never set

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-12-28 6:34 AM

I have a discovery stm8s003k board and when I tested a program for cco capability it seems cco will never be stable and program always remain in line:

while(CLK_GetFlagStatus(CLK_FLAG_CCORDY) == FALSE);

code and more explain is in detail.

I tested it with below code and I even change pre-scalers for lower and higher frequency, I also check it with external crystal (and change the code) but it remains in

while(CLK_GetFlagStatus(CLK_FLAG_CCORDY) == FALSE);

forever.

When I debug the code and step over in debugger environment after the program enables CCOEN bit the output will start and frequency is just true. but both flag CCOBSY remains set (CCOR=0x69 in debugger) and it always remain in while loop.

when i try cco out put in stm 32 it is also seem unstable for example every thing is ok but every 8 clock one of clock has a little change in frequency or duty cycle ,what is problem with mco or cco section? thanks for reply.

My code is:

#include "STM8S.h"

#define LED_pin GPIO_PIN_0

#define LED_port GPIOD

void setup(void);

void clock_setup(void);

void GPIO_setup(void);

void main(void)

{

setup();

GPIO_WriteLow(LED_port, LED_pin);

while(TRUE){};

}

void setup(void)

{

clock_setup();

GPIO_setup();

}

void clock_setup(void)

{

CLK_DeInit();

CLK_HSECmd(DISABLE);

CLK_LSICmd(DISABLE);

CLK_HSICmd(ENABLE);

while(CLK_GetFlagStatus(CLK_FLAG_HSIRDY) == FALSE);

CLK_ClockSwitchCmd(ENABLE);

CLK_HSIPrescalerConfig(CLK_PRESCALER_HSIDIV8);

CLK_SYSCLKConfig(CLK_PRESCALER_CPUDIV4);

CLK_ClockSwitchConfig(CLK_SWITCHMODE_AUTO, CLK_SOURCE_HSI,

DISABLE, CLK_CURRENTCLOCKSTATE_ENABLE);

CLK_PeripheralClockConfig(CLK_PERIPHERAL_I2C, DISABLE);

CLK_PeripheralClockConfig(CLK_PERIPHERAL_SPI, DISABLE);

CLK_PeripheralClockConfig(CLK_PERIPHERAL_UART1, DISABLE);

CLK_PeripheralClockConfig(CLK_PERIPHERAL_AWU, DISABLE);

CLK_PeripheralClockConfig(CLK_PERIPHERAL_ADC, DISABLE);

CLK_PeripheralClockConfig(CLK_PERIPHERAL_TIMER1, DISABLE);

CLK_PeripheralClockConfig(CLK_PERIPHERAL_TIMER2, DISABLE);

CLK_PeripheralClockConfig(CLK_PERIPHERAL_TIMER4, DISABLE);

CLK_CCOConfig(CLK_OUTPUT_CPU);

CLK_CCOCmd(ENABLE);

while(CLK_GetFlagStatus(CLK_FLAG_CCORDY) == FALSE); //it remains here forever

}

void GPIO_setup(void)

{

GPIO_DeInit(LED_port);

GPIO_Init(LED_port, LED_pin, GPIO_MODE_OUT_OD_HIZ_FAST);

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-12-28 7:35 AM

> but every 8 clock one of clock has a little change in frequency or duty cycle

Sounds like a quantization error introduced by the logic analyzer sample rate. Post a screenshot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-05 12:32 PM

Had the same problem with CCO. The cpu is running on HSE with a crystal and AWU fed with the LSI

while(CLK_GetFlagStatus(CLK_FLAG_CCORDY) == FALSE); never exits when you select the CPU clock (divided or not) for CCO. It works fine when LSI is selected.

My temporary (dirty) solution was to simply comment out the check, as I simply wanted to see if the HSE stops in Active Halt Mode (it does).

I'll check later why the CCO flag does not work as expected.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-06 12:04 PM

thanks for reply:)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-07 2:24 AM

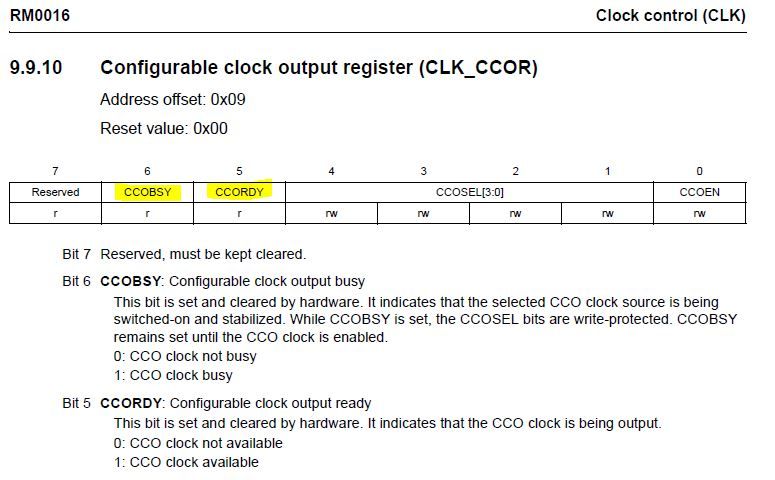

Well, I think I found the problem in stm8s_clk.h.

In RM0016 you can see that CCOBSY and CCORDY are in the upper nibble of CLK_CCOR

I commented out the offending lines in stm8s_clk.h and replaced them with what I think they should be.

typedef enum {

CLK_FLAG_LSIRDY = (uint16_t)0x0110, /*!< Low speed internal oscillator ready Flag */

CLK_FLAG_HSIRDY = (uint16_t)0x0102, /*!< High speed internal oscillator ready Flag */

CLK_FLAG_HSERDY = (uint16_t)0x0202, /*!< High speed external oscillator ready Flag */

CLK_FLAG_SWIF = (uint16_t)0x0308, /*!< Clock switch interrupt Flag */

CLK_FLAG_SWBSY = (uint16_t)0x0301, /*!< Switch busy Flag */

CLK_FLAG_CSSD = (uint16_t)0x0408, /*!< Clock security system detection Flag */

CLK_FLAG_AUX = (uint16_t)0x0402, /*!< Auxiliary oscillator connected to master clock */

//CLK_FLAG_CCOBSY = (uint16_t)0x0504, /*!< Configurable clock output busy */

//CLK_FLAG_CCORDY = (uint16_t)0x0502 /*!< Configurable clock output ready */

CLK_FLAG_CCOBSY = (uint16_t)0x0540, /*!< Configurable clock output busy */

CLK_FLAG_CCORDY = (uint16_t)0x0520 /*!< Configurable clock output ready */

}CLK_Flag_TypeDef;And now all options for CCO on my STM8S103F3 work as I expect them to.

EDIT: STM8S103K3 (LQFP32)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-19 1:20 AM

- Atomic variable for scheduler question in STM32 MCUs Embedded software

- Code Review Request: Integrating MotionFX with ASM330LHH, LIS2DH12, and LIS3MDL over SPI in MEMS (sensors)

- ADC continuous mode in STM32 MCUs Products

- ENTER_CRITICAL_SECTION() : behavior of __disable_irq() in STM32 MCUs Embedded software

- Clear Interrupts Prior to sleep confusion in STM32 MCUs Products