- STMicroelectronics Community

- STM32 MPUs

- STM32 MPUs Products

- Re: ETH1 doesn't work on stm32mp135

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ETH1 doesn't work on stm32mp135

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-05-25 02:45 AM

Hi, I designed a board with stm32mp135 and YT8531 phy chip. The ETH1 is not working and ETH2 is work good. They all output 125Mhz from phy to mac. But the ETH1 has reset dma failed. I had measure the 125Mhz is correct on phy side.

Below is my dts code

ð1 {

status = "okay";

pinctrl-0 = <ð1_rgmii_pins_a>;

pinctrl-1 = <ð1_rgmii_sleep_pins_a>;

pinctrl-names = "default", "sleep";

phy-mode = "rgmii-id";

max-speed = <1000>;

phy-handle = <&phy0_eth1>;

mdio1 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "snps,dwmac-mdio";

phy0_eth1: ethernet-phy@1 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <1>;

reset-gpios = <&gpiog 10 GPIO_ACTIVE_LOW>;

reset-assert-us = <10000>;

reset-deassert-us = <1000>;

};

};

};

ð2 {

status = "okay";

pinctrl-0 = <ð2_rgmii_pins_a>;

pinctrl-1 = <ð2_rgmii_sleep_pins_a>;

pinctrl-names = "default", "sleep";

phy-mode = "rgmii-id";

max-speed = <1000>;

phy-handle = <&phy0_eth2>;

phy-supply = <&v3v3_ao>;

mdio1 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "snps,dwmac-mdio";

phy0_eth2: ethernet-phy@2 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <2>;

reset-gpios = <&gpiog 9 GPIO_ACTIVE_LOW>;

reset-assert-us = <10000>;

reset-deassert-us = <1000>;

};

};

};

eth1_rgmii_pins_a: eth1_mx-0 {

pins1 {

pinmux = <STM32_PINMUX('D', 7, AF10)>, /* ETH1_RX_CLK */

<STM32_PINMUX('A', 7, AF11)>, /* ETH1_RX_CTL */

<STM32_PINMUX('B', 0, AF11)>, /* ETH1_RXD2 */

<STM32_PINMUX('B', 1, AF11)>, /* ETH1_RXD3 */

<STM32_PINMUX('C', 4, AF11)>, /* ETH1_RXD0 */

<STM32_PINMUX('C', 5, AF11)>; /* ETH1_RXD1 */

bias-disable;

};

pins2 {

pinmux = <STM32_PINMUX('A', 2, AF11)>; /* ETH1_MDIO */

bias-disable;

drive-push-pull;

slew-rate = <0>;

};

pins3 {

pinmux = <STM32_PINMUX('B', 11, AF11)>, /* ETH1_TX_CTL */

<STM32_PINMUX('C', 1, AF11)>, /* ETH1_GTX_CLK */

<STM32_PINMUX('C', 2, AF11)>, /* ETH1_TXD2 */

<STM32_PINMUX('E', 5, AF10)>, /* ETH1_TXD3 */

<STM32_PINMUX('F', 12, AF11)>, /* ETH1_CLK125 */

<STM32_PINMUX('G', 2, AF11)>, /* ETH1_MDC */

<STM32_PINMUX('G', 13, AF11)>, /* ETH1_TXD0 */

<STM32_PINMUX('G', 14, AF11)>; /* ETH1_TXD1 */

bias-disable;

drive-push-pull;

slew-rate = <2>;

};

};

eth1_rgmii_sleep_pins_a: eth1_sleep_mx-0 {

pins {

pinmux = <STM32_PINMUX('D', 7, ANALOG)>, /* ETH1_RX_CLK */

<STM32_PINMUX('A', 2, ANALOG)>, /* ETH1_MDIO */

<STM32_PINMUX('A', 7, ANALOG)>, /* ETH1_RX_CTL */

<STM32_PINMUX('B', 0, ANALOG)>, /* ETH1_RXD2 */

<STM32_PINMUX('B', 1, ANALOG)>, /* ETH1_RXD3 */

<STM32_PINMUX('B', 11, ANALOG)>, /* ETH1_TX_CTL */

<STM32_PINMUX('C', 1, ANALOG)>, /* ETH1_GTX_CLK */

<STM32_PINMUX('C', 2, ANALOG)>, /* ETH1_TXD2 */

<STM32_PINMUX('C', 4, ANALOG)>, /* ETH1_RXD0 */

<STM32_PINMUX('C', 5, ANALOG)>, /* ETH1_RXD1 */

<STM32_PINMUX('E', 5, ANALOG)>, /* ETH1_TXD3 */

<STM32_PINMUX('F', 12, ANALOG)>, /* ETH1_CLK125 */

<STM32_PINMUX('G', 2, ANALOG)>, /* ETH1_MDC */

<STM32_PINMUX('G', 13, ANALOG)>, /* ETH1_TXD0 */

<STM32_PINMUX('G', 14, ANALOG)>; /* ETH1_TXD1 */

};

};

eth2_rgmii_pins_a: eth2_mx-0 {

pins1 {

pinmux = <STM32_PINMUX('A', 8, AF11)>, /* ETH2_RXD3 */

<STM32_PINMUX('A', 12, AF11)>, /* ETH2_RX_CTL */

<STM32_PINMUX('E', 2, AF10)>, /* ETH2_RXD1 */

<STM32_PINMUX('F', 4, AF11)>, /* ETH2_RXD0 */

<STM32_PINMUX('H', 6, AF12)>, /* ETH2_RXD2 */

<STM32_PINMUX('H', 11, AF11)>; /* ETH2_RX_CLK */

bias-disable;

};

pins2 {

pinmux = <STM32_PINMUX('B', 6, AF11)>; /* ETH2_MDIO */

bias-disable;

drive-push-pull;

slew-rate = <0>;

};

pins3 {

pinmux = <STM32_PINMUX('E', 6, AF11)>, /* ETH2_TXD3 */

<STM32_PINMUX('F', 6, AF11)>, /* ETH2_TX_CTL */

<STM32_PINMUX('F', 7, AF11)>, /* ETH2_TXD0 */

<STM32_PINMUX('G', 1, AF10)>, /* ETH2_TXD2 */

<STM32_PINMUX('G', 3, AF10)>, /* ETH2_GTX_CLK */

<STM32_PINMUX('G', 5, AF10)>, /* ETH2_MDC */

<STM32_PINMUX('G', 11, AF10)>, /* ETH2_TXD1 */

<STM32_PINMUX('H', 2, AF13)>; /* ETH2_CLK125 */

bias-disable;

drive-push-pull;

slew-rate = <2>;

};

};

eth2_rgmii_sleep_pins_a: eth2_sleep_mx-0 {

pins {

pinmux = <STM32_PINMUX('A', 8, ANALOG)>, /* ETH2_RXD3 */

<STM32_PINMUX('A', 12, ANALOG)>, /* ETH2_RX_CTL */

<STM32_PINMUX('B', 6, ANALOG)>, /* ETH2_MDIO */

<STM32_PINMUX('E', 2, ANALOG)>, /* ETH2_RXD1 */

<STM32_PINMUX('E', 6, ANALOG)>, /* ETH2_TXD3 */

<STM32_PINMUX('F', 4, ANALOG)>, /* ETH2_RXD0 */

<STM32_PINMUX('F', 6, ANALOG)>, /* ETH2_TX_CTL */

<STM32_PINMUX('F', 7, ANALOG)>, /* ETH2_TXD0 */

<STM32_PINMUX('G', 1, ANALOG)>, /* ETH2_TXD2 */

<STM32_PINMUX('G', 3, ANALOG)>, /* ETH2_GTX_CLK */

<STM32_PINMUX('G', 5, ANALOG)>, /* ETH2_MDC */

<STM32_PINMUX('G', 11, ANALOG)>, /* ETH2_TXD1 */

<STM32_PINMUX('H', 2, ANALOG)>, /* ETH2_CLK125 */

<STM32_PINMUX('H', 6, ANALOG)>, /* ETH2_RXD2 */

<STM32_PINMUX('H', 11, ANALOG)>; /* ETH2_RX_CLK */

};

};Solved! Go to Solution.

- Labels:

-

STM32MP15 Lines

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-05-25 08:16 AM - edited 2023-11-20 04:37 AM

Hi @Community member ,

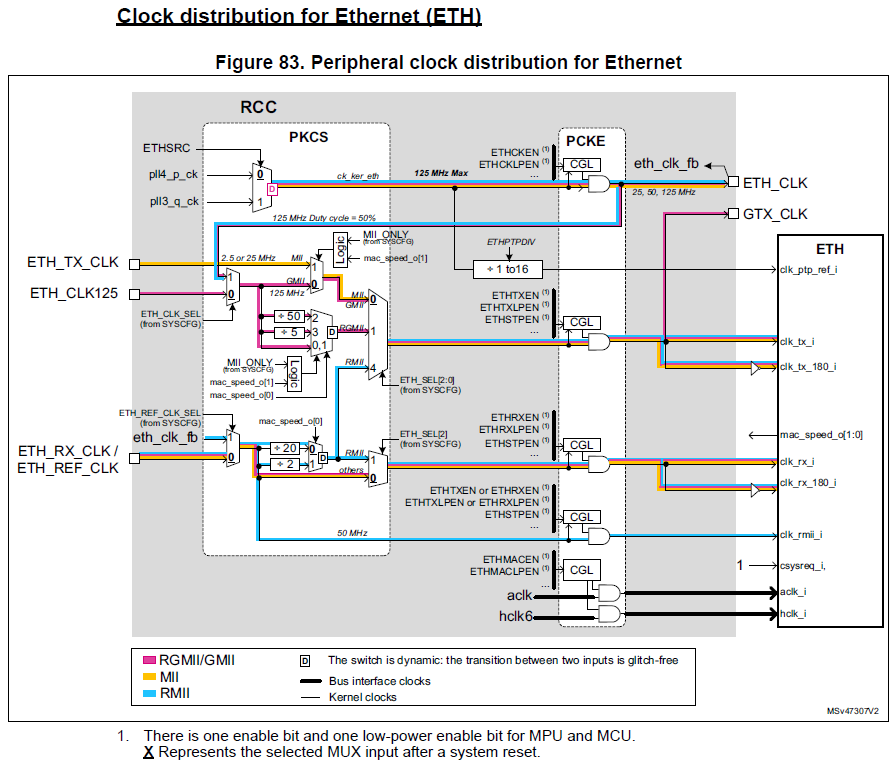

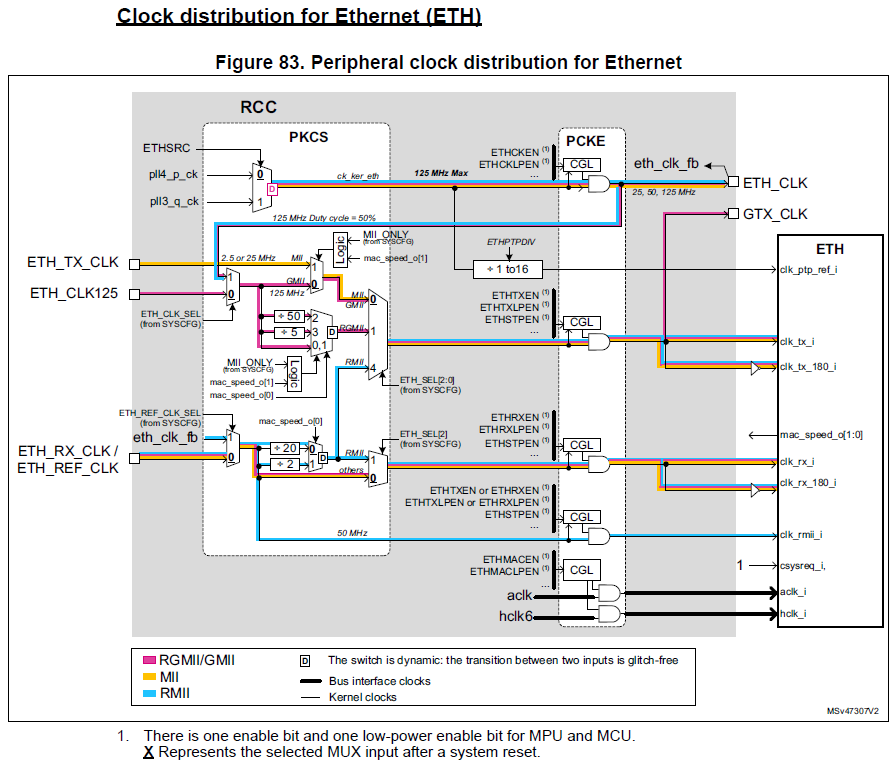

You are right, usually this 'reset dma' error is linked to a missing clock to the ETH GMAC IP inputs during initialization.

Please have a look to https://wiki.st.com/stm32mpu/wiki/Ethernet_device_tree_configuration#RGMII_with_Crystal_on_PHY-2C_CLK125_from_PHY_-28Reference_clock_-28standard_RGMII_clock_name-29_is_provided_by_a_Phy_Crystal-29

If this suit your use case.

Maybe have a look to Reference Manual RCC section to understand the RGMII clock possible paths.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-05-25 08:16 AM - edited 2023-11-20 04:37 AM

Hi @Community member ,

You are right, usually this 'reset dma' error is linked to a missing clock to the ETH GMAC IP inputs during initialization.

Please have a look to https://wiki.st.com/stm32mpu/wiki/Ethernet_device_tree_configuration#RGMII_with_Crystal_on_PHY-2C_CLK125_from_PHY_-28Reference_clock_-28standard_RGMII_clock_name-29_is_provided_by_a_Phy_Crystal-29

If this suit your use case.

Maybe have a look to Reference Manual RCC section to understand the RGMII clock possible paths.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-05-25 09:21 AM

please also check the Getting started with STM32MP13x lines hardware development - Application note for correct connection of the 2 ETH on the board if needed.

- eMMC external loader sources for stm32mp1 in STM32 MPUs Software development tools

- Strange PANIC message on STM32MP135F in STM32 MPUs Products

- USB Composite in STM32MP135 in STM32 MPUs Products

- Boot from USB OTG pins on STM32MP131 in STM32 MPUs Boards and hardware tools

- stm32mp135D fails to find rootfs when booting from SD Card in STM32 MPUs Products