- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Wireless

- STM32WB55 SRAM2 retention

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32WB55 SRAM2 retention

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-10 6:48 AM

Using the suggestions from https://community.st.com/t5/stm32-mcus-wireless/stm32wb-sram2a-what-is-the-size-that-can-be-used-without/m-p/176847

I can now address the remaining non secure SRAM2A as BKUP_RAM. During runtime this seems to work just fine, but after Standby the RAM is still cleared, even though RRS in PWR->CR3 is and remains set. Is this a "feature" of the wireless stack or am I doing something else wrong?

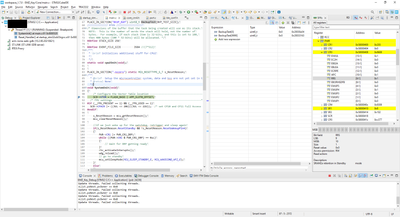

As you can see in the screenshot, I stopped the operation on SystemInit. This is called before any loading of RAM data, so my canaries (expected are 0x55 at the beginning and 0xAA at the end of the test array) should even still be alive if NOLOAD didn't work for some reason, but instead I have clean zeros(! no random data) throughout the array.

Solved! Go to Solution.

- Labels:

-

STM32WB series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-13 12:11 AM

So I checked my option bytes for the nth time and finally realized that SRAM2RST has inverse logic. So enabling that bit leads to disabling the SRAM2 reset, and I finally keep my data.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-13 12:11 AM

So I checked my option bytes for the nth time and finally realized that SRAM2RST has inverse logic. So enabling that bit leads to disabling the SRAM2 reset, and I finally keep my data.

- Implementing STM32L4S5ZIT6 Bootloader with a Memory Marker in STM32 MCUs Products

- Nucleo STM32WB55: Firmware delete and Firmware Upgrade fails with FUS_STATE_ERR_UNKNOWN in STM32 MCUs Wireless

- STM32U5 Backup SRAM in standby in STM32 MCUs Products

- How to configure AHB and APB for STOP Mode on STM32L4? in STM32 MCUs Products