- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Wrong FLASH_ACR->LATENCY bit in stm32f103xe.h?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Wrong FLASH_ACR->LATENCY bit in stm32f103xe.h?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-22 04:22 AM

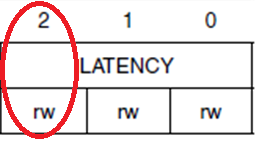

Section 3.3.3 of the reference manual (RM0008, Rev16) for STM32F10XXX MCUs explains in the register description for FLASH_ACR->LATENCY:

Bits 2:0 LATENCY: Latency

These bits represent the ratio of the SYSCLK (system clock) period to the Flash access time.

000 Zero wait state, if 0 < SYSCLK≤ 24 MHz

001 One wait state, if 24 MHz < SYSCLK ≤ 48 MHz

010 Two wait states, if 48 MHz < SYSCLK ≤ 72 MHz

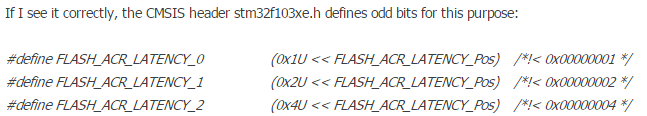

If I see it correctly, the CMSIS header stm32f103xe.h defines odd bits for this purpose:

#define FLASH_ACR_LATENCY_0 (0x1U << FLASH_ACR_LATENCY_Pos) /*!< 0x00000001 */

#define FLASH_ACR_LATENCY_1 (0x2U << FLASH_ACR_LATENCY_Pos) /*!< 0x00000002 */ #define FLASH_ACR_LATENCY_2 (0x4U << FLASH_ACR_LATENCY_Pos) /*!< 0x00000004 */In previous versions of the header file this wasn't the case, even thought the documentation of these bits appears a bit confusing:

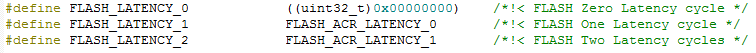

* @file stm32f10x.h

* @author MCD Application Team * @version V3.5.0 * @date 11-March-2011...

#define FLASH_ACR_LATENCY ((uint8_t)0x03) /*!< LATENCY[2:0] bits (Latency) */

#define FLASH_ACR_LATENCY_0 ((uint8_t)0x00) /*!< Bit 0 */#define FLASH_ACR_LATENCY_1 ((uint8_t)0x01) /*!< Bit 0 */#define FLASH_ACR_LATENCY_2 ((uint8_t)0x02) /*!< Bit 1 */Best regards

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-23 04:12 AM

Hi Peter,

Those code lines are used to define every bit's position in FLASH_ACR register (bit-field LATENCY).

To configure the wait states, you should use the definitions in ''stm32f1xx_hal_flash.h'' file.

If this answers your request,

please click on correct

:)

.Khouloud.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-03 05:58 AM

Hi Khouloud,

thanks for your response! I'm still not 100% convinced. Also as bitfield, this definition

#define FLASH_ACR_LATENCY_2 (0x4U << FLASH_ACR_LATENCY_Pos) /*!< 0x00000004 */

would represent bit number two, right? But the reference manual states that bit number one must be set for two wait states.

Best regardsPeter- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-05 06:19 AM

Hi Peter,

You should not confuse between ''FLASH_LATENCY_2'' and ''FLASH_ACR_LATENCY_2''.

FLASH_LATENCY_2: is what you should use to configure two latency cycles (2 wait states).

It's the second parameter needed by ''HAL_RCC_ClockConfig'' function.

FLASH_ACR_LATENCY_2: is the bit definition of bit N°2 in the ''FLASH_ACR '' register.

I hope this is clear now.

Regards,

Khouloud.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-06 01:03 AM

Hi Khouloud,

thanks again! Yes it's clear now. I was just too confused about the definitions in V3.5.0 of the header file which worked differently.

Cheers

Peter

- Input capture / Frequency Measurement error on STM32U545REQ in STM32 MCUs Products

- My board can no longer run the program I uploaded to it earlier in STM32CubeIDE (MCUs)

- STM32WLxx DFU Error in STM32 MCUs Wireless

- STM32H725ZGT6 suspected error in documentation - interrupt table in STM32 MCUs Products

- STM32CubeIDE .cproject vs CMake files in STM32CubeIDE (MCUs)