- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: What is the difference control between ODR and...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

What is the difference control between ODR and BSRRL(BSRRH)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-06 10:13 PM

Hi

I'm currently working with STM32F429I-disco kit.

and testing about gpio control.

the below code is working well.

But I want to know

int main(void){RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOG, ENABLE);RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOA, ENABLE); // GPIOG->CRL = 0x2800;GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0 ;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN;GPIO_InitStructure.GPIO_OType = GPIO_OType_PP;GPIO_InitStructure.GPIO_Speed = GPIO_Speed_100MHz;GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_NOPULL;GPIO_Init(GPIOA, &GPIO_InitStructure); GPIO_InitStructure.GPIO_Pin = GPIO_Pin_14;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_OUT;GPIO_InitStructure.GPIO_OType = GPIO_OType_PP;GPIO_InitStructure.GPIO_Speed = GPIO_Speed_100MHz;GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_NOPULL;GPIO_Init(GPIOG, &GPIO_InitStructure);&sharpusing ODR

while (1)

{ if(GPIOA->IDR & GPIO_Pin_0) GPIOG->ODR =GPIO_Pin_14;else GPIOG->ODR = 0x00;}}

&sharpusing BSRR

while (1)

{if(GPIOA->IDR & GPIO_Pin_0)GPIOG->BSRRL = GPIO_Pin_14;elseGPIOG->BSRRH = 0xFFFF;}

My question is what is the difference between

ODR and BSRR?

#gpioSolved! Go to Solution.

- Labels:

-

GPIO-EXTI

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-07 10:41 PM

I am not sure how to make you understand, but plz let me refer you to the following great resource:

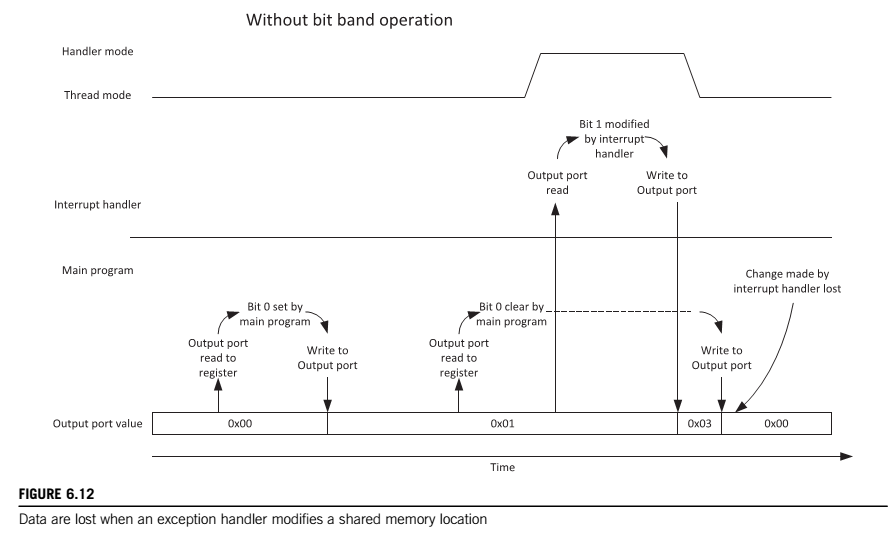

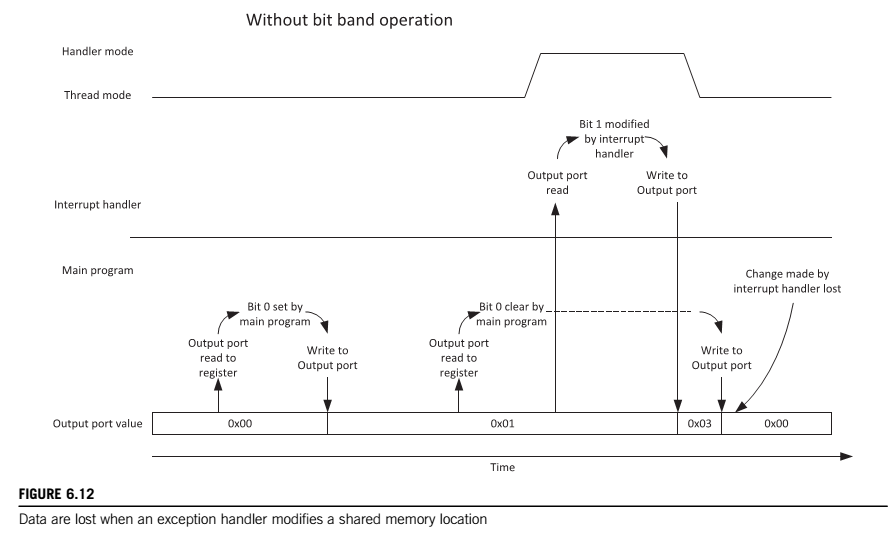

FIGURE 6.12 from The Definitive Guide to ARM Cortex-M3 and Cortex-M4 Processors, by Yiu.

Here is a similar problem if you use ODR register. You don't need to care about the meaning of bit band for the moment.

You may try to figure out how the problem is solved if BSRR register is used.

Zt.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-07 12:30 AM

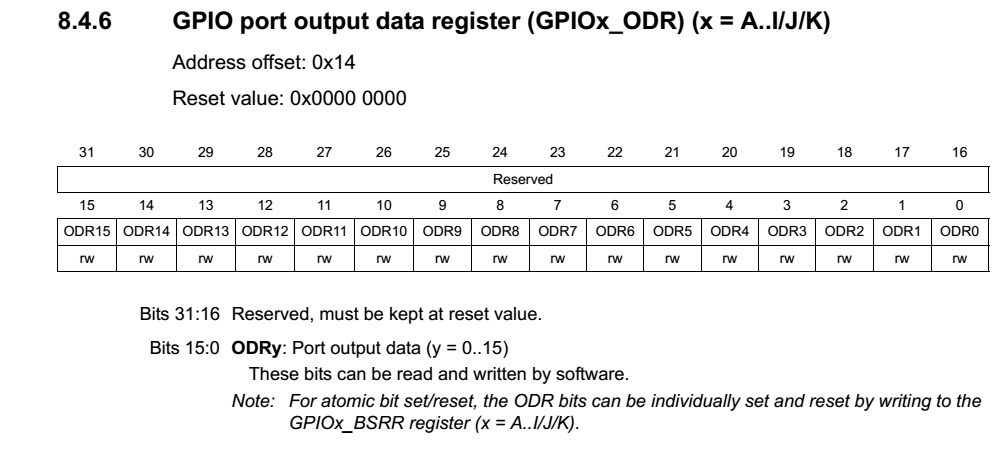

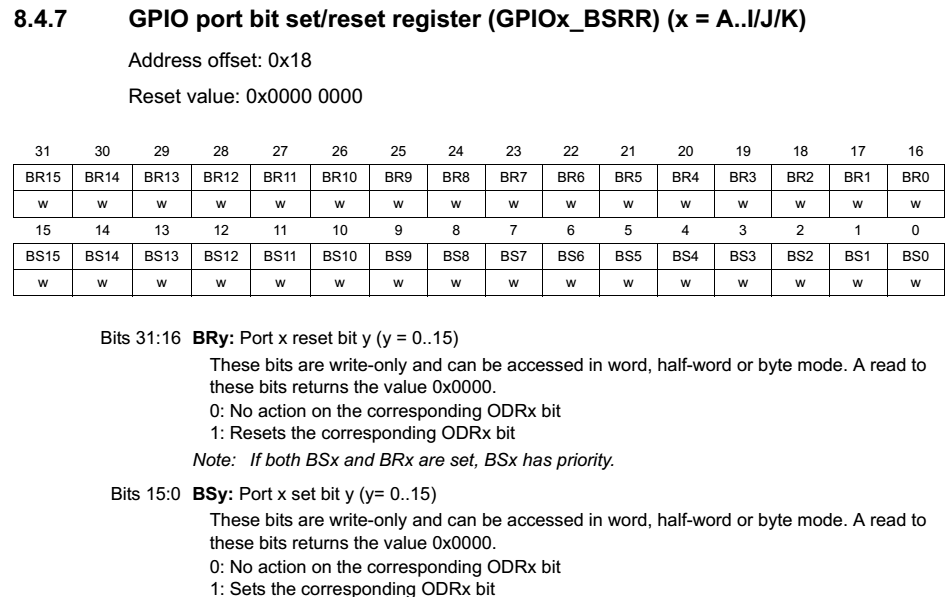

ODR is read/write register, BSRR is write only, and has no effect if you set a bit to zero.

So that an atomic bit operation is done through BSRR register.

Hope that helps you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-07 12:31 AM

Hi

dv2

,The bit set reset register (GPIOx_BSRR) is a 32-bit register which allows the application to set and reset each individual bit in the output data register (GPIOx_ODR).

The bit set reset register has twice the size of GPIOx_ODR. To each bit in GPIOx_ODR, correspond two control bits in GPIOx_BSRR: BSRR(i) and BSRR(i+SIZE). When written to 1, bit BSRR(i) sets the corresponding ODR(i) bit. When written to 1, bit BSRR(i+SIZE) resets the ODR(i) corresponding bit.

Writing any bit to 0 in GPIOx_BSRR does not have any effect on the corresponding bit in GPIOx_ODR. If there is an attempt to both set and reset a bit in GPIOx_BSRR, the set action takes priority.

Using the GPIOx_BSRR register to change the values of individual bits in GPIOx_ODR is a “one-shot�? effect that does not lock the GPIOx_ODR bits. The GPIOx_ODR bits can always be accessed directly. The GPIOx_BSRR register provides a way of performing atomic bitwise handling.

There is no need for the software to disable interrupts when programming the GPIOx_ODR at bit level: it is possible to modify one or more bits in a single atomic AHB1 write access.

-Nesrine-

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-07 11:30 AM

Could you please letting me know some more example for understanding?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-07 10:41 PM

I am not sure how to make you understand, but plz let me refer you to the following great resource:

FIGURE 6.12 from The Definitive Guide to ARM Cortex-M3 and Cortex-M4 Processors, by Yiu.

Here is a similar problem if you use ODR register. You don't need to care about the meaning of bit band for the moment.

You may try to figure out how the problem is solved if BSRR register is used.

Zt.

- MotorControl Workbench Issues in STM32 MCUs Motor control

- Difference in Generated Files: STM32Cube.AI GUI vs. CLI in STM32CubeMX (MCUs)

- HAL TIM IC Capturecallback on multiple functions in STM32 MCUs Embedded software

- STM32G0B1 USB Host not working in STM32 MCUs Products

- Two NUCLEO-H755ZI-Q boards acting differently in STM32 MCUs Boards and hardware tools