- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- TIMx_SMCR->SMS - 3 bits or 4?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

TIMx_SMCR->SMS - 3 bits or 4?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-02 10:28 AM

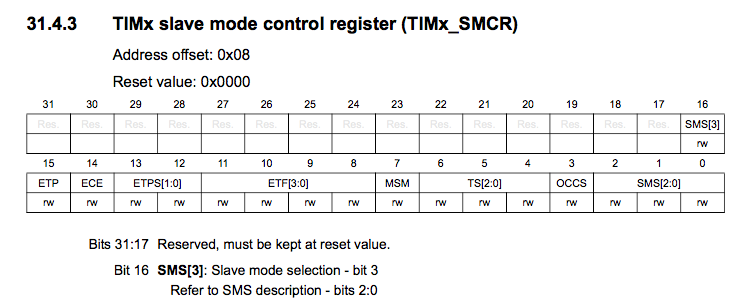

RM0351, section 31.4.3 slave mode control register.

chart shows SMS[2:0] but the description of SMS on page 1032 describes a 4 bit number

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-02 10:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-02 06:36 PM

,

,

Dopey me. That SMS[3] is the fourth bit. They even made it easy in the header file

♯ define TIM_SMCR_SMS_Pos , , , , , , , , , (0U) , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , ,

,

♯ define TIM_SMCR_SMS_Msk , , , , , , , , , (0x10007U <,<, TIM_SMCR_SMS_Pos) , , , , , , , , , , , , , , /*!<, 0x00010007 */,

♯ define TIM_SMCR_SMS , , , , , , , , , , , , , TIM_SMCR_SMS_Msk , , , , , , , , , , , , , , , , , , , , , , , , , , , , /*!<,SMS[2:0] bits (Slave mode selection) */,

♯ define TIM_SMCR_SMS_0 , , , , , , , , , , , (0x00001U <,<, TIM_SMCR_SMS_Pos) , , , , , , , , , , , , , , /*!<, 0x00000001 */,

♯ define TIM_SMCR_SMS_1 , , , , , , , , , , , (0x00002U <,<, TIM_SMCR_SMS_Pos) , , , , , , , , , , , , , , /*!<, 0x00000002 */,

♯ define TIM_SMCR_SMS_2 , , , , , , , , , , , (0x00004U <,<, TIM_SMCR_SMS_Pos) , , , , , , , , , , , , , , /*!<, 0x00000004 */,

♯ define TIM_SMCR_SMS_3 , , , , , , , , , , , (0x10000U <,<, TIM_SMCR_SMS_Pos) , , , , , , , , , , , , , , /*!<, 0x00010000 */this is how I ended up working around:

, , switch(((*(uint32_t*)&,TIM3->,SMCR &, TIM_SMCR_SMS) >,>, TIM_SMCR_SMS_Pos) )

,

, , {,

, , case 0b00000000000000000000000000000000: printf(''Slave mode disabled\r\n''), break,,

, , case 0b00000000000000000000000000000001: printf(''Encoder mode 1\r\n''), break,,

, , case 0b00000000000000000000000000000010: printf(''Encoder mode 2\r\n''), break,,

, , case 0b00000000000000000000000000000011: printf(''Encoder mode 3\r\n''), break,,

, , case 0b00000000000000000000000000000100: printf(''Reset mode\r\n''), break,,

, , case 0b00000000000000000000000000000101: printf(''Gated mode\r\n''), break,,

, , case 0b00000000000000000000000000000110: printf(''Trigger mode\r\n''), break,,

, , case 0b00000000000000000000000000000111: printf(''External clock mode 1\r\n''), break,,

, , case 0b00000000000000010000000000000000: printf(''Combined reset + trigger mode\r\n''), break,,

, , }- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-04 03:09 AM

Btw. the same applies for TIMx_CCMRy.OCzM - the OCzM[3] bit is further up in the same register.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-04 08:00 AM

Hi

doe.john.016

,A request is raised internally to add a note saying that the other bit is described as standalone in the same register.

Thanks

Waclawek.Jan

for your proposal.-Amel

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- STM32F756VGH6 SPI pins are not responding in STM32 MCUs Products

- Delays between SPI transfers on STM32F411 using DMA in STM32 MCUs Embedded software

- Which communication interface is suitable to observer motor current? (fast/real-time ) in STM32 MCUs Motor control

- STM32U585 need help with getting ADC -> DMA working in trivial case. in STM32 MCUs Products

- Migrating from STM32H755 to STM32H733, UART breaks in STM32 MCUs Embedded software