- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- sym32f767igt read phy chip lan8720 any register =0...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

sym32f767igt read phy chip lan8720 any register =0x00?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-29 08:39 AM

I try add eth support under uboot with my stm32f767igt board,my dts file as below:

ethernet_mii: mii@0 {

pins { pinmux = <STM32F746_PG13_FUNC_ETH_MII_TXD0_ETH_RMII_TXD0>, <STM32F746_PG14_FUNC_ETH_MII_TXD1_ETH_RMII_TXD1>, <STM32F746_PB11_FUNC_ETH_MII_TX_EN_ETH_RMII_TX_EN>, <STM32F746_PA2_FUNC_ETH_MDIO>, <STM32F746_PC1_FUNC_ETH_MDC>, <STM32F746_PA1_FUNC_ETH_MII_RX_CLK_ETH_RMII_REF_CLK>, <STM32F746_PA7_FUNC_ETH_MII_RX_DV_ETH_RMII_CRS_DV>, <STM32F746_PC4_FUNC_ETH_MII_RXD0_ETH_RMII_RXD0>, <STM32F746_PC5_FUNC_ETH_MII_RXD1_ETH_RMII_RXD1>; slew-rate = <2>; }; };&mac {

status = ''okay''; pinctrl-0 = <ðernet_mii>; phy-mode = ''rmii''; phy-handle = <&phy0>; snps,reset-gpio = <&gpiof 9 1>; /*PF9<-->ETH_RESET*/ snps,reset-active-low; snps,reset-delays-us = <1000 1000 1000>; mdio0 { #address-cells = <1>; #size-cells = <0>; compatible = ''snps,dwmac-mdio''; phy0: ethernet-phy@0 { reg = <0>; }; };};i conformed mdio relate pin PC1 and PA2 with AF11 function as below

and GPIOC and GPIOA are enabled as

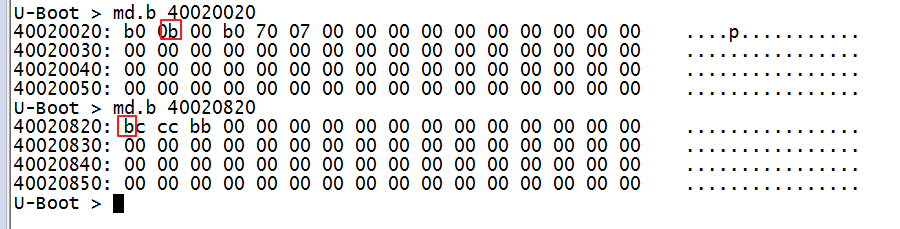

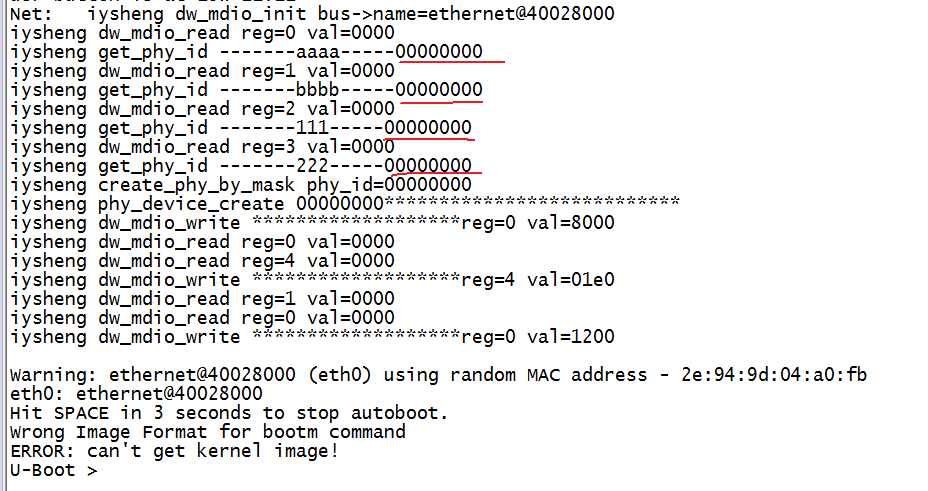

but whichever register of the phy chip i read i always get 0x0000,,,

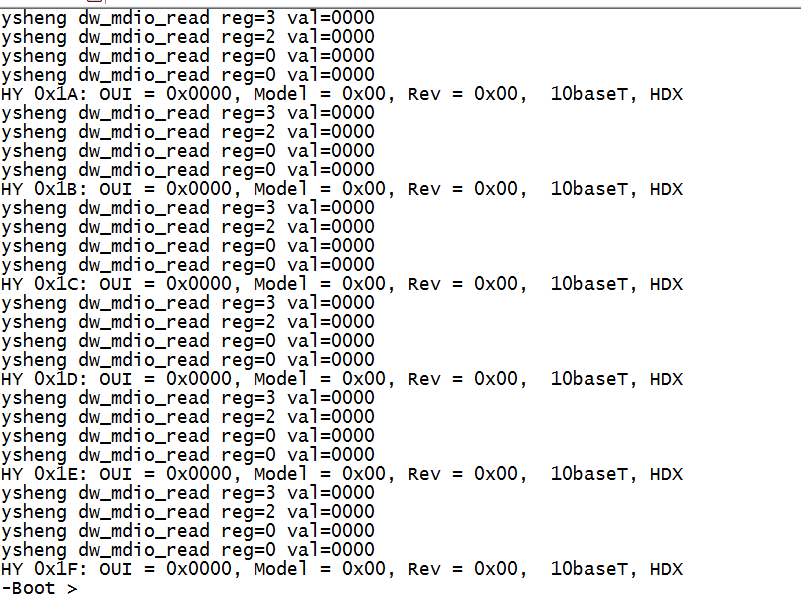

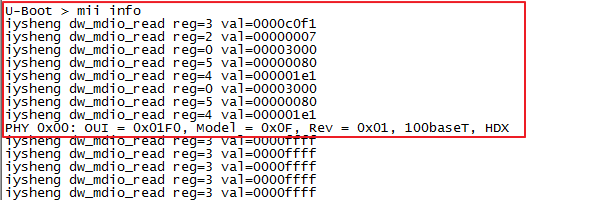

i try use mii info command test again ,i get the same

Besides,once i insert the cable to router,the link on rj45 both light,but i could not ping server success.

what's wrong maybe?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-30 08:54 AM

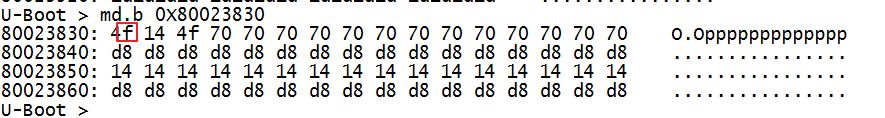

after i change a phy chip lan8720a,now i could get registers in this phy,as below

but when i try to test the net , i get this message

and i see hal code,in func HAL_StatusTypeDef HAL_ETH_Init(ETH_HandleTypeDef *heth)

there is some code just like

tickstart = HAL_GetTick();

#if 1 /* Wait for software reset */ while (((heth->Instance)->DMABMR & ETH_DMABMR_SR) != (uint32_t)RESET) { /* Check for the Timeout */ tickstart = HAL_GetTick(); if((HAL_GetTick() - tickstart ) > ETH_TIMEOUT_SWRESET) { heth->State= HAL_ETH_STATE_TIMEOUT; /* Process Unlocked */ __HAL_UNLOCK(heth); /* Note: The SWR is not performed if the ETH_RX_CLK or the ETH_TX_CLK are not available, please check your external PHY or the IO configuration */ return HAL_TIMEOUT; } }#endifAs the comment said

The SWR is not performed if the ETH_RX_CLK or the ETH_TX_CLK are

not available, please check your external PHY or the IO configuration.

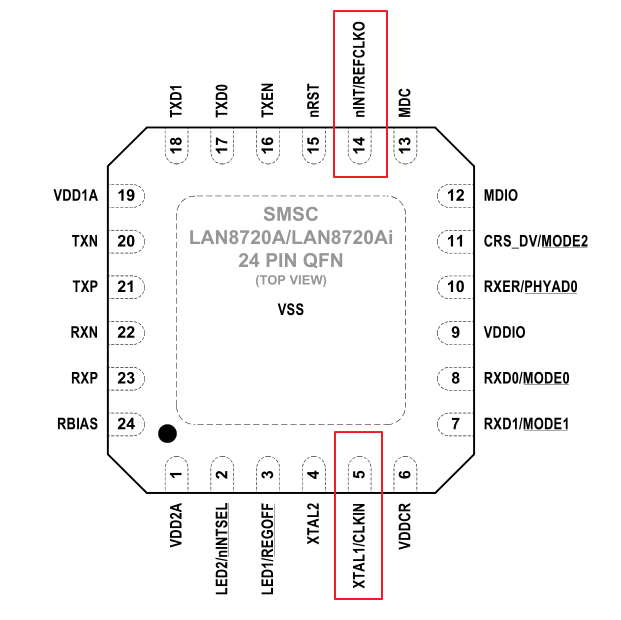

what's the ETH_TX_CLK or ETH_RX_CLK,i could not get these pins in phy chip lan8720a,the pins of lan8720a just below

is these pins of ETH_TX_CLK and ETH_RX_CLK be relate with pin5 and pin14??