STM32H563VI Octo-SPI interface dummy cycles

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-11 1:48 AM

Hi,

someone can explain me how to calculate the "dummy cycles" number reading an external flash qspi such as the Winbond W25Q64JV ?

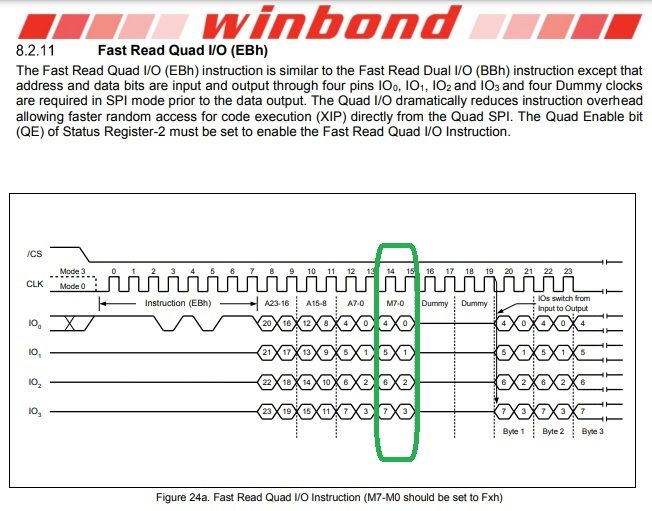

I have to read in qspi mode with the Fast Read Quad I/O (EBh) command in SDR mode. The flash memory datasheet asks for 4 dummy cycles between addressing and data available.

In effect, if I set 4 dummy cycles, the first data byte is lost. On the contrary, if I set 6 dummy cycles, the read operation success.

I think this depend to the Pre-drive time, but how can I calculate the effective dummy cycles to apply, to be sure that all the reading will be done correctly ?

Thank you.

Solved! Go to Solution.

- Labels:

-

OctoSPI

-

STM32H5 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-11 8:13 AM

It's 6 in your case because you fail to deal with the Mode/Alternate bits that the part is expecting...

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-11 3:57 AM

Hello @Ez ,

I think that you can contact the manufacture for more details because the datasheet refer to 4 dummy cycles

"four Dummy clocks are required in SPI mode prior to the data output"

Foued

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-11 6:40 AM

Hi Foued,

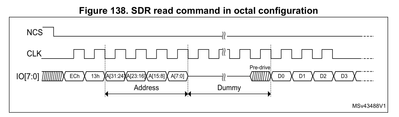

thank you for your answer but in the STM32H5xx reference manual there is this figure about the dummy cycles

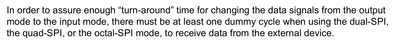

As you can see, the Dummy Cycles contains a "Pre-Drive" time that is not described in anywhere, and moreover in the same Reference Manual, speaking about the Dummy Cycle Phase, I found this:

What does it mean "there must be at least one dummy cycle" ....?? Means one, two, three, or so many?

In my opinion, I have to clarify this before ask to the memory manufacturer, because it is not clear.

Moreover, I found some drivers for the same flash memory on GitHub where the dummy cycles has been increased to 6, I think for the same reason:

https://github.com/Crazy-Geeks/STM32-W25Q-QSPI/blob/main/Library/w25q_mem.c

where you can find:

/**

* @brief W25Q Read any 8-bit data from raw addr

* Read any 8-bit data from preffered chip address

*

* @note Address is in [byte] size

* @note Be carefull with page overrun

* @PAram[out] buf Pointer to data to be written (single or array)

* @PAram[in] data_len Length of data (1..256)

* @PAram[in] rawAddr Start address of chip's cell

* @return W25Q_STATE enum

*/

W25Q_STATE W25Q_ReadRaw(u8_t *buf, u16_t data_len, u32_t rawAddr) {

if (data_len > 256 || data_len == 0)

return W25Q_PARAM_ERR;

while (W25Q_IsBusy() == W25Q_BUSY)

w25q_delay(1);

QSPI_CommandTypeDef com;

com.InstructionMode = QSPI_INSTRUCTION_1_LINE; // QSPI_INSTRUCTION_...

#if MEM_FLASH_SIZE > 128U

com.Instruction = W25Q_FAST_READ_QUAD_IO_4B; // Command

com.AddressSize = QSPI_ADDRESS_32_BITS;

#else

com.Instruction = W25Q_FAST_READ_QUAD_IO; // Command

com.AddressSize = QSPI_ADDRESS_24_BITS;

#endif

com.AddressMode = QSPI_ADDRESS_4_LINES;

com.Address = rawAddr;

com.AlternateByteMode = QSPI_ALTERNATE_BYTES_NONE;

com.AlternateBytes = QSPI_ALTERNATE_BYTES_NONE;

com.AlternateBytesSize = QSPI_ALTERNATE_BYTES_NONE;

com.DummyCycles = 6;

com.DataMode = QSPI_DATA_4_LINES;

com.NbData = data_len;

com.DdrMode = QSPI_DDR_MODE_DISABLE;

com.DdrHoldHalfCycle = QSPI_DDR_HHC_ANALOG_DELAY;

com.SIOOMode = QSPI_SIOO_INST_EVERY_CMD;

if (HAL_QSPI_Command(&hqspi, &com, HAL_QSPI_TIMEOUT_DEFAULT_VALUE)

!= HAL_OK)

return W25Q_SPI_ERR;

if (HAL_QSPI_Receive(&hqspi, buf, HAL_QSPI_TIMEOUT_DEFAULT_VALUE) != HAL_OK)

return W25Q_SPI_ERR;

return W25Q_OK;

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-11 8:13 AM

It's 6 in your case because you fail to deal with the Mode/Alternate bits that the part is expecting...

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-11 8:25 AM

you are a genius :grinning_face: