- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32G0x Series Filter downcounter on External Clo...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32G0x Series Filter downcounter on External Clock Source for Advanced Control Timer 1 (TIM1)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-05 8:58 PM - last edited on 2023-12-06 2:04 AM by Sarra.S

Hi,

I am using an event as an external clock input into the Advanced Control Timer (TIM1) on a STM32G0x series MCU.

For my application it will be nice to low pass filter the signal using the internal "Filter Downcounter" in the chip.

I don't understand the internal digital logic of the filter, nor can I find detail on how this Digital Filter works (Flip-Flops, ect...), but here is my theory and hopefully someone can please share more detail or correct me.

This is the diagram in the datasheet.

Inputs into filter: N(amount of samples) , fdts(counter frequency), ETRP(event signal)

I assume, the filter is a type of counter. If there is N consecutive events in the logic signal for 1/f(dts) time. The output logic signal of the filter contains one pulse.

After 1/f(dts) time, the filter resets the internal counter. Or if there is no event triggered in the signal, when an event was expected. Hence, it has to be, consecutive positive event triggers.

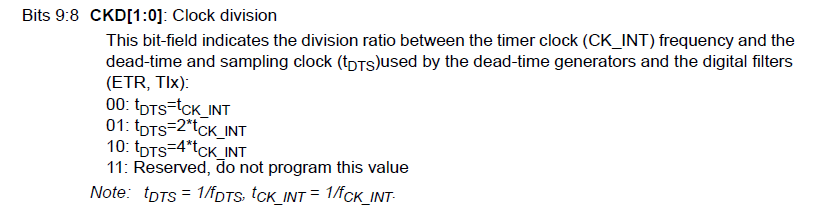

Now, f(dts) is related to the input clock frequency in the Datasheet. The sampling period of this t(dts), can be set to the following settings in the datasheet:

Solved! Go to Solution.

- Labels:

-

STM32G0 Series

-

TIM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-06 2:11 AM

Hello @danielbathtub, welcome to ST Community

You can refer to 1.4.1 Filtering stage chapter in AN4776

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-06 2:11 AM

Hello @danielbathtub, welcome to ST Community

You can refer to 1.4.1 Filtering stage chapter in AN4776

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Tip: A super-simple circuit for auto-detecting hardware variants in STM32 MCUs Products

- Trigger ADC with TIM2 TRGO not showing correct timing in STM32 MCUs Products

- Fixed number (5) of Pulses triggered by external event. (STM32H753ZI to ADS8556) in STM32 MCUs Products

- Nucleo F767ZI - Led LD4 RED in Others: STM32 MCUs related

- Fail to load images from the SD card in STM32 MCUs TouchGFX and GUI