Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F7 SPI pulsed mode problem: how to leave ...

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F7 SPI pulsed mode problem: how to leave NSS low

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-08-19 1:01 AM

Posted on August 19, 2016 at 10:01 Does anyone have an idea how to keep NSS low during all the 32 clocks? I already tried many things and hoped that the ''Sequence handling'' handled this... Software handling of NSS is NOT a solution in my case.Thanks,Andre #stm32f7-spi

Does anyone have an idea how to keep NSS low during all the 32 clocks? I already tried many things and hoped that the ''Sequence handling'' handled this... Software handling of NSS is NOT a solution in my case.Thanks,Andre #stm32f7-spi

Hi all,

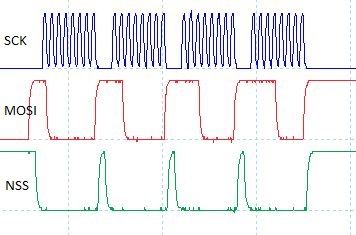

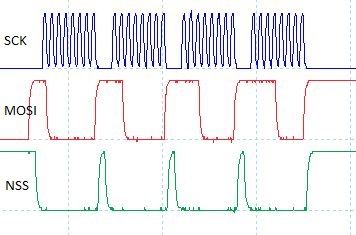

I need to interface with a common IC which needs to have the NSS low during the complete message of 32 clocks. I have all working, DMA is triggered by a timer and fills the SPI data register with the complete message. However I don't succeed in having the NSS stay low during the 32 clocks. NSS goes high after 8 or 16 clocks (depending on datasize): Does anyone have an idea how to keep NSS low during all the 32 clocks? I already tried many things and hoped that the ''Sequence handling'' handled this... Software handling of NSS is NOT a solution in my case.Thanks,Andre #stm32f7-spi

Does anyone have an idea how to keep NSS low during all the 32 clocks? I already tried many things and hoped that the ''Sequence handling'' handled this... Software handling of NSS is NOT a solution in my case.Thanks,Andre #stm32f7-spi

Labels:

- Labels:

-

STM32F7 Series

2 REPLIES 2

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-09-23 8:34 AM

Posted on September 23, 2016 at 17:34

Hello,

It looks like the NSS pulse mode is enabled (NSSP=1) or the driver disable the SPI after each data transaction. These both setting can force the NSS HW to high between data. If the DMA is set to sure number of data greater than one, the SPI transaction (clock signal) should be continuous suppose there is no other DMA or bus activity limiting the DMA sufficient bandwidth to handle the SPI events at time (it depends mainly on ratio between SCK clock and the IP pclk clock).RegardsOptions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-11-04 2:59 AM

Posted on November 04, 2016 at 10:59

Hi,

I have investigated a lot. It is just not possible to have a number of clocks different from 8 or 16. This makes the peripheral useless for a lot of SPI components (like EEprom). Fortunately in my case the external SPI ADC I use just ignores extra clocks.Hope this peripheral will be better next time.Best regards

Related Content

- STM32F7 - USB problems on Windows - SMT32Cube FW_F7 V.1.17.2 broken? in STM32 MCUs Products

- Problem in STM32F7 with ethernetif.c provided by STM32CubeIDE 1.7.0 in STM32 MCUs Embedded software

- Output comparison pulse problem in STM32 MCUs Products

- SPI SSD1306 and I2C MPU6050 on stm32f103c8t6 in STM32 MCUs Boards and hardware tools

- I2C Gives No Output in STM32 MCUs Products