- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: stm32f4 pwm input example

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

stm32f4 pwm input example

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-04-26 11:44 AM

Is anybody willing to explain

''The TIMxCLK frequency is set to SystemCoreClock/4 (Hz). The Prescaler is 0, so the

counter clock is SystemCoreClock/2 (Hz).

'' Is TIMxCLK not the same as counter clock? Thanks, Jonathan- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-04-26 01:12 PM

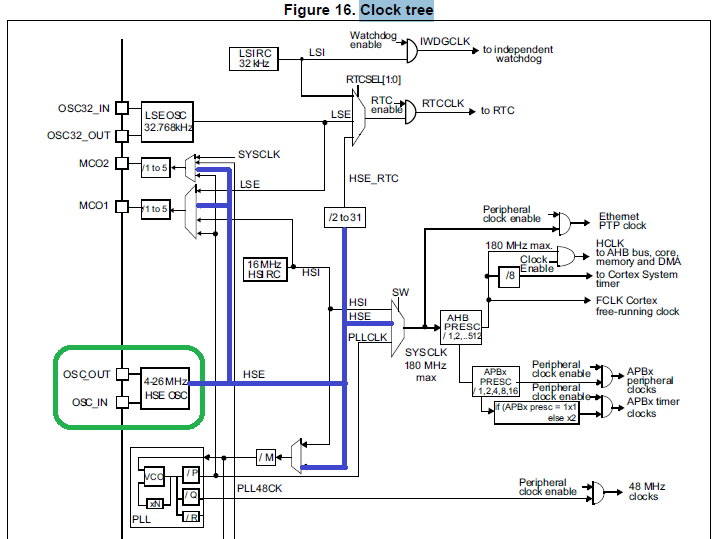

Where APB is SYSCLK/4 then TIMCLK = SYSCLK/2

See the Clock Tree Diagram in the Reference ManualUp vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-04-26 02:23 PM

ok I think I understand that diagrram now, or at least the bit of it that goes

HSE/HSI/PLLCLK -> AHB PRESC -> if(APBx presc = 1x1, else x2) -> APBx timer clocks. I'd tried to study diagram that a while back when I was much more of a beginner and was utterly baffled. My understanding of the clocks is that a few different, options HSE, LSE and something else I can't remember off the top of my head can be chosen as the system clock, then all other clocks are derivative of that. I would have expected the clock tree diagram to look more like a family tree though.. ie, one or more sources at the top like ancestors, then each of those producing a derivative ones, which produce generations derivative generations. Clive, do you think you could point out to me where the 'top generation', ie the HSE oscillator would be found in this clock diagram? I think if I get that I can get closer to understanding the whole thing. Just a quadrant of it with a label, you don't have to be too specific.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-04-26 03:19 PM

The other source is the PLL, which is a clock multiplier (basically divides a reference clock down to 1 MHz, and uses that in a feedback loop to control a faster voltage controlled oscillator)

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-04-26 03:28 PM

I cannot express how helpful that diagram is, thankyou so much!! Looking at it now I don't know how I missed the HSE OSC to start with.

- Inline assembly code - register usage in STM32CubeIDE (MCUs)

- Input capture / Frequency Measurement error on STM32U545REQ in STM32 MCUs Products

- external interrupt in stm32f107 in STM32 MCUs Products

- Timer XOR ON / Hall Sensor Mode Edge Trigger Problem in STM32 MCUs Products

- 8 simultaneous frequency measurements up to 2MHz on STM32U545REQ in STM32 MCUs Products