- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32 SDADC phase delay ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32 SDADC phase delay ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-28 12:14 AM

Hello everybody

Does anyone have experience with the SDADC of the STM32F373?

I have the following question:

Theoretically, my phase delay would have to be at a

Sampling frequency of 50kHz and output to the 12bit DAC be as follows:

My input circuit OPAmp with filter 2700Ohm 330pF = ca.1us

SDADC input (impedance 120kOhm 0.7pF) delay = ca.T = 120kOhm * 0.7pF = 0.08us

SDADC conversion time = 1 / fs = 1 / 50kHz = 20us

DAC (with buffer) tSettling = 4us

Reconstruction filter RC = 680Ohm 10nF = delay = 680Ohm x 10nF = ca.7us

My C-code measured = 5us

Total:

1us

+

0.08us

+

20us

+

4us

+

5 us

+

7us

=

37.08usBut I measure with Oscilloscope 55us!

I reach the required bandwidth of 10kHz.

On the KO I see too

the 5 steps at 10kHz (50kHz sampling rate).

That proves that I have correctly configured the SDADC.

I just can not get the theoretical phase time.

Can someone tell me where this difference comes from?

Greeting

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-28 1:34 AM

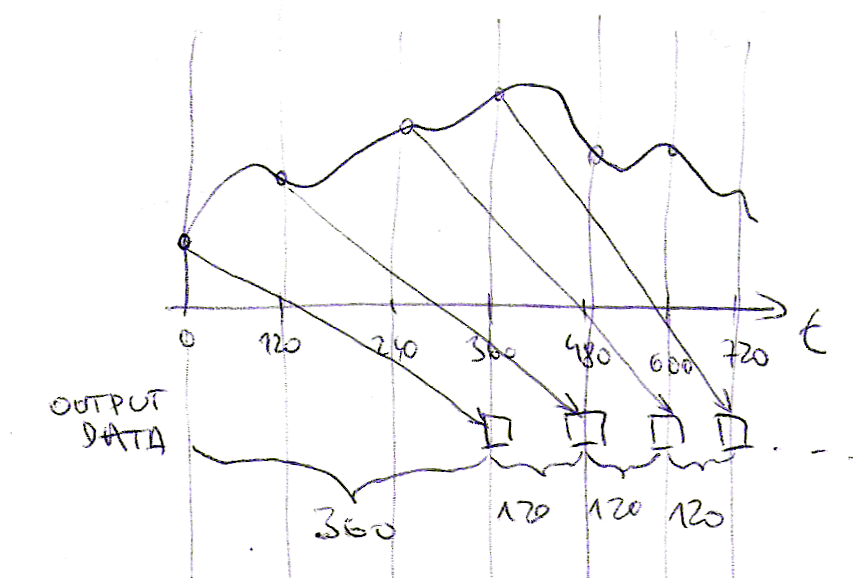

This is not a plain SAR ADC, and the digital filters inherent to sigma-delta conversion involve delays. The 120 cycles per conversion is the maximum sampling rate, but the samples are pipelined (i.e. they pass through several filtering stages) making up the 360 cycles total delay/'latency'. As the RM puts it in Continuous and fast continuous modes subchapter:

In fast continuous mode (FAST=1), the first conversion takes still 360 SDADC clocks, but then each subsequent conversion finishes in 120 SDADC clocks.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-28 1:46 AM

Thank you for the fast answer.

Then I have to calculate this as follows?

Conversion time + filter time

Conversion time = 20us at 50ksps

Filter time = 20us (120 cycles at 6MHz SADC Clocks)

Total = 40us?

I thought the conversion time is sync.filter included.

?

Greeting

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-28 7:01 AM

Hmm ?

I have my SDADC in fast continuous mode.It's simply takes 360 cycles until the signal propagates from analog input to the output data buffer, i.e. 60us, that's all.

But this is only the first conversion takes ! Each subsequent conversion finishes in 120 SDADC clocks i.e 20us !When conversion time = Analog signal from analog Input to the Output data buffer then i don't understand my measurment result i.e 55us !When conversion time = only sample time without sync filter then my result is correct20us conversion time + 20 us time sync Filter = 40us + 15us (Input filter, Code, Output filter).what is conversion time ? with filter i.e. 20us

or without filter ? i.e. 40us

(I think it is whitout filter and not signal propagates from analog input to the output data buffer)

Greeting

Roger

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-28 7:24 AM

No. It's simply takes 360 cycles until the signal propagates from analog input to the output data buffer, i.e. 60us, that's all.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-28 5:47 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-01 12:35 AM

Hi JW

Thank you very much. Now i understand.

Conversion time is each subsequent conversion and = 20usBut Attention! The first conversion need 360 cycles at the phase time minimum result = 60usConclusion:

For the Phase time (Latency) only the filter is responsible.

Thanks

Roger

- Phase shifted pulses using pwm in STM32 MCUs Products

- SPI communication issue on STM32F103RB (sort of buffer over/underun) in STM32 MCUs Embedded software

- SPI Sending and Receiving Extra Bytes in STM32 MCUs Products

- Hall sensor offset angle identification with Motor Pilot and oscilloscope in STM32 MCUs Motor control

- SPI CR1 bit SPE will not set in STM32 MCUs Products