- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Regarding IWDG maximum timeout duration to res...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Regarding IWDG maximum timeout duration to reset in STM32F446RET6.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-20 02:40 AM

Hi!

I have working on the watch Dog implementation in STM32F446RET6.The board which I have used is NUCLEO-F446RET6.

I have followed the below mentioned steps,

1. Enabled the IWDG in system core using CubeMX of STM32CubeIDE. (which takes the LSI frequency for the IWDG as 32KHz in Clock Configuration.)

2. In Parameters settings of IWDG, Set the Pre-scalar divider as 256 and the down counter reload value as 4095 which are the maximum values to produce the time out of 32.768 seconds as per the reference manual.

I have theoretically calculated the duration using the formula,

IWDG_Time= [(Reload Value+1)*(Pre-scalar value)]/ LSI frequency

=[(4095+1)*256]/32000

= 32.768 seconds

- I didn't refresh the watch dog timer anywhere. So, As per the program the system need to be reset in 32.768 seconds (approximately 33 secs). But in real case, the system got reset after the 39 seconds or in 40 secs. Why this delay of 7 - 8 seconds is taken for the system reset?

- Similarly, I have configured the Pre-scalar divider as 256 and the down counter reload value as 2249 which are the values to produce the time out of 18 seconds.

IWDG_Time= [(Reload Value+1)*(Pre-scalar value)]/ LSI frequency

=[(2249+1)*256]/32000

= 18 seconds

-- In this case the system resets after the 22 seconds but not in 18 secs? Why?

I have attached the output screenshot for your reference.

Kindly, suggest the solution for this!

Thanks in Advance!!!

Solved! Go to Solution.

- Labels:

-

STM32F4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-20 05:05 AM - edited 2023-09-20 05:32 AM

Hello again @AnnakkiliArumugam

The LSI value is ~32KHz but with a very large tolerance. That's why we say LSI is a 32KHz frequency oscillator with a tolerance of ~47%.

To solve this issue, you can use this .

Best regards.

II

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-20 03:26 AM

Welcome @AnnakkiliArumugam, to the community!

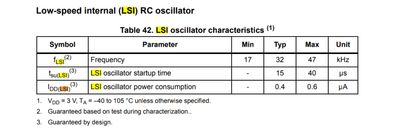

Well, you have not taken into account the tolerance of the LSI given in the data sheet of the STM32F446RET6. Unfortunately, no free-running oscillator with 0% tolerance has been developed yet, so the STM32F446RET6 has a tolerance of approx. ±47% given in section 6.3.10, table 42.

In your example you have determined a tolerance of (22s-18s)/18s = 22.2%, which is perfectly within the maximum tolerance.

Does it answer your question?

Regards

/Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-20 03:35 AM - edited 2023-09-20 04:49 AM

Hello @AnnakkiliArumugam

As you can see her:

Those values are for exactly 32khz LSI frequency .But looking to the datasheet we can find that the LSI frequency can be any value between 17KHz and 47KHz.

That means, the IWDG_time can change between ~22s and ~61s for Pre-scalar=256 and down counter reload=4095.

Best regards.

II

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-20 04:46 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-20 04:52 AM

You're welcome!

If the problem is solved, please click Accept as Solution for your preferred answer. This will help other users find that answer faster.

Regards

/Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-20 04:53 AM

Thanks for the response!

But looking to the datasheet we can find that the LSI frequency can be any value between 17KHz and 47KHz.

--- This means that the LSI value of the Controller oscillates between 17KHz and 47KHz and it is not a constant value. Is my understanding is correct?

--- Then why in the stm32f4xx_hal_conf.h file it is mentioned as 32KHz? (and also in clock configuration of CubeMX).

Is there any solution to achieve the nearest interval?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-20 05:05 AM - edited 2023-09-20 05:32 AM

Hello again @AnnakkiliArumugam

The LSI value is ~32KHz but with a very large tolerance. That's why we say LSI is a 32KHz frequency oscillator with a tolerance of ~47%.

To solve this issue, you can use this .

Best regards.

II

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-20 05:21 AM

Hello @AnnakkiliArumugam,

You can always calibrate LSI as it can be internally remapped to TIM5-CH4 in order to adjust the IWDG clock.

To do that:

* Configure the TIM5 to remap internally the TIM5 CH4 Input Capture to the LSI clock output.

* Enable the TIM5 Input Capture interrupt: after one cycle of LSI clock, the period value is stored in a variable and compared to the HCLK clock to get its real value.

You can find this method implementation in the STM32F4 Cube package - IWDG example.

Hope that helps!

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-20 06:06 AM

@Peter BENSCH @Issamos So, how often do we have to calibrate LSI? Does it remain stable in every specific unit or varies with supply voltage, temperature etc.?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-20 06:09 AM

Okay!

I am searching for the solution to achieve the desired timeout interval. While gone through it I have found about this!

#define TIM_TIM5_LSI TIM_OR_TI4_RMP_0 /*!< TIM5 TI4 is connected to LSI */

Does we can achieve the desired timeout interval using this timer 5 by calculating the LSI frequency ?