- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Problem with SPI_SLAVE_DMA transmision

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Problem with SPI_SLAVE_DMA transmision

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-11 9:29 AM

hi st

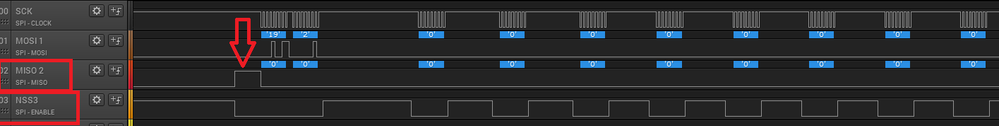

I have problem using spi slave with dma

i use stm32f746 as slave to transmit data to master pc

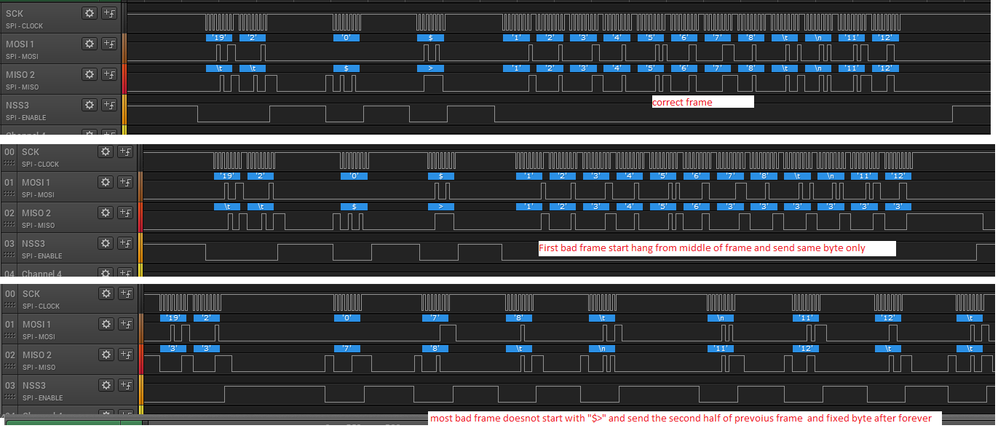

i send for test fixed frame start with check char ''$>'' to sync timing then slave should send 12 bytes ( 1-12)

problem many times i got error that frame sent upto middle correct then fixed byte to end and in next frame slave send other frame missing from previous frame and continue with fixed byte for ever as much as master send clock

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-11 4:04 PM

are you using the DMA ?

the DMA buffer must be left alone until it completes.

then you can reset data within the buffer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-12 2:25 AM

IMPORTANT NOTICE

the bad frame start with MISO high once start communication ( once nss set low by master) which mean that slave say to master I'm not ready and that good option to make sync

normal frames start with MISO low

why and how this happen ?? what does that mean really ?

- How to use PWM with DMA (STL Libraries) in STM32 MCUs Embedded software

- Copying data from External Flash doesn't copy into buffer using generated TouchGFXGeneratedDataReader.cpp on STM32F4? in STM32 MCUs TouchGFX and GUI

- Problem with USART3 and Systick in STM32 MCUs Products

- STM32F407VGT6 SPI1 receive problem. in STM32 MCUs Products