- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Modifying Open drain and push pull frequency of I3...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Modifying Open drain and push pull frequency of I3C messages with appropriate duty cycle

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-11 7:57 AM

Hi

How can we define separate frequency for open drain and push pull modes for I3C communication ?

In the documentation only the low phase is mentioned but for high phase there's no separate option for OD & PP modes.

Ideally I would like to do something like this

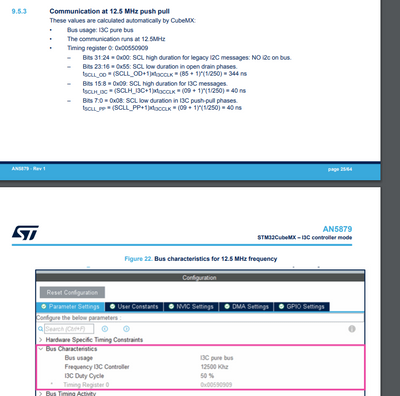

<Context> I am working with STM32H5RB03 as the controller and a MEMS sensor as the target. I want to do I3C communication at 12.5Mhz but the initial OD phase should have much lower frequency(<2Mhz) in order for the sensor to ACK(respond). I'm a newbie so might make basic mistakes while formulating my question, please ask if you need more clarity.

Solved! Go to Solution.

- Labels:

-

Documentation

-

I3C

-

STM32H5 series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-12 4:45 AM - edited 2023-09-12 4:46 AM

Hello @Asfand ,

Sorry ! The I3C_CtrlTimingComputation function is not available in the I3C files .

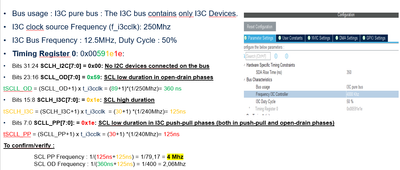

But you can just define LL_I3C_CtrlBusConfTypeDef and add the parameters for the new timing :

This mean, configure the parameters SDAHoldTime, WaitTime, SCLPPLowDuration, SCLI3CHighDuration, SCLODLowDuration, SCLI2CHighDuration, BusFreeDuration, BusIdleDuration in the LL_I3C_CtrlBusConfTypeDef structure through i3c Init structure.

Then call :

HAL_I3C_Ctrl_BusCharacteristicConfig(I3C_HandleTypeDef *hi3c,const LL_I3C_CtrlBusConfTypeDef *pConfig);

Foued

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-11 8:13 AM - edited 2023-09-11 8:15 AM

Hello @Asfand ,

You can't define separate frequency for open drain and push pull modes for I3C communication in STM32CubeMx.

So after generate code, you should set the desired frequency

/* Set bus speed to 1MHz for example*/

LL_I3C_CtrlBusConfTypeDef CtrlBusConf;

/* Calculate the new timing for Controller */

I3C_CtrlTimingComputation(&CtrlBusConf,

HAL_RCCEx_GetPeriphCLKFreq(RCC_PERIPHCLK_I3C1),

1000000,

0,

50,

I3C_PURE_I3C_BUS);

/* Update Controller Bus characteristic */

HAL_I3C_Ctrl_BusCharacteristicConfig(&hi3c1, &CtrlBusConf);

after you can change it, before the transfer :

/* Set bus speed to 5MHz for example*/

/* Calculate the new timing for Controller */

I3C_CtrlTimingComputation(&CtrlBusConf,

HAL_RCCEx_GetPeriphCLKFreq(RCC_PERIPHCLK_I3C1),

5000000,

0,

50,

I3C_PURE_I3C_BUS);

/* Update Controller Bus characteristic */

HAL_I3C_Ctrl_BusCharacteristicConfig(&hi3c1, &CtrlBusConf);

Hope it helps!

Foued

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-12 2:44 AM

Hi @Foued_KH

Thanks for the prompt reply.

I am using STM32CUBEIDE and it can not recognize the function 'I3C_CtrlTimingComputation' & definition 'I3C_PURE_I3C_Bus'. I have generated the example 'I3C Controller Inband interrupt' from STM32CubeMx by selecting appropriate board(not using example from Git repo).

Are these functions/definitions not included when we generate code from STM32CubeMx? If yes, can you point to the specific files I should look for ?

For ref:

Let me know If I'm missing something.

Regards,

Asfand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-12 4:45 AM - edited 2023-09-12 4:46 AM

Hello @Asfand ,

Sorry ! The I3C_CtrlTimingComputation function is not available in the I3C files .

But you can just define LL_I3C_CtrlBusConfTypeDef and add the parameters for the new timing :

This mean, configure the parameters SDAHoldTime, WaitTime, SCLPPLowDuration, SCLI3CHighDuration, SCLODLowDuration, SCLI2CHighDuration, BusFreeDuration, BusIdleDuration in the LL_I3C_CtrlBusConfTypeDef structure through i3c Init structure.

Then call :

HAL_I3C_Ctrl_BusCharacteristicConfig(I3C_HandleTypeDef *hi3c,const LL_I3C_CtrlBusConfTypeDef *pConfig);

Foued

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-12 6:19 AM

Hi @Foued_KH

I'm able to change the frequency in between the code which is very useful. Thanks!

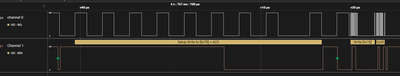

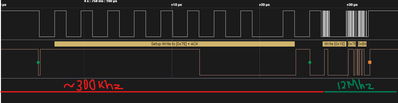

But the initial question the remains i.e. In one I3C message how can the frequency be varied by the controller in OD and PP phase. Usually the other controllers do this by themselves(not sure how, might be some sort of config).

The LL_I3C_CtrlBusConfTypeDef type has the same parameters as mentioned in the first post and lack the separate High Duration parameter for OD & PP.

Maybe following snap will help in clarification of what I'm trying to say.

Thank you for the support.

Regards,

Asfand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-12 6:40 AM

Hello @Asfand

I will share with you an example and let me know if this is helpful or not :

Best Regards,

Foued

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 1:44 AM - edited 2023-09-13 2:02 AM

EDIT: With uneven duty cycle, i am able to achieve the desired functionality. So turns out these parameters are good enough.

Also the according to info on wikipedia this change in duty cycle is normal/must.

"

SCL is a conventional digital clock signal, driven with a push-pull output by the current bus controller during data transfers. (Clock stretching, a frequently used I²C feature, is not supported.) In transactions involving I²C target devices, this clock signal generally has a duty cycle, of approximately 50%, but when communicating with known I3C targets, the bus controller may switch to a higher frequency and/or alter the duty cycle so the SCL high period is limited to at most 40 ns.

"

Hi @Foued_KH

Thank you for the reply.

After reading the definitions. I do not see a way of producing the desired waveform using these parameters. As the frequency difference(for ex:12Mhz-500khz) would result in a stretched duty cycle.

Regards,

Asfand

- STM32F779NI - suffix for 216 MHz or 200 MHz maximum frequency ? in STM32 MCUs Products

- Debug STLink GDB Server v.1.3.0 - PARSE ERROR: Argument: -cp in STM32CubeIDE for Visual Studio Code (MCUs)

- Real audio frequency and error between selected in SAI for the STM32N6 showing 0 in STM32CubeMX (MCUs)

- CubeMx(v6.17) Cross Selector Displays MCU Operating Frequency Incorrectly in STM32CubeMX (MCUs)

- STM32 USB CDC: How to Customize COM Port Friendly Name on Windows Without INF File? in STM32 MCUs Products