- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: LSE Oscillator on STM32F769

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LSE Oscillator on STM32F769

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-04-04 09:32 AM

I have a custom board with a STM32F769 and I am having problems getting the low speed LSE oscillator running. I am using CubeMX 4.19 to generate the low level code. In order to get the oscillator to run I need to set the drive strength to high with the LSEDRV bits in the RCC_BDCR.

However the code produced by CubeMX calls HAL_RCC_OscConfig() before setting the drive strength. The call to HAL_RCC_OscConfig() fails with a timeout because the LSERDY bit never gets set, because the oscillator isn't running.

I can add

__HAL_RCC_LSEDRIVE_CONFIG(RCC_LSEDRIVE_HIGH);

to stm32f7xx_hal_rcc.c but this will get over written next time I generate code from CubeMX.

As a side issue the reference manual suggests at 5.3.20 that the LSEDRV bits are not part of the backup domain but I don't seem to be able to write to them until the backup domain write accesses have been enabled.

Any ideas what to do next? I know I could change the 32.768kHz to a low capacitance device that works with low drive strength but I am looking for a software solution.

Thanks,

Mike

Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-05 09:35 AM

Hello!

Are you sure that the generated code is correct?

In my project the LSEDRV is not set with __HAL_RCC_LSEDRIVE_CONFIG(RCC_LSEDRIVE_HIGH), because

at that point there is no write access to Backup domain.

I have solved this bug by moving __HAL_RCC_LSEDRIVE_CONFIG(RCC_LSEDRIVE_HIGH)

to right after the 'Backup domain Write protection disable' code section in the

HAL_RCC_OscConfig function

.I think this is a bug in

STM32CubeMX which has to be solved.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-04-04 10:09 AM

STM32 devices have historically been very intolerant of 9 and 12pF crystals (slow to start, don't start)

You will get far fewer headaches using 6-7pF crystals.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-04-04 10:13 AM

Hi

Forster.Mike

,I suggest you to have a look to

application note and the user manual to havemore details on compatible crystals and hardware techniques on PCB.

-Nesrine-

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-04-05 06:00 AM

Thanks Nesrine and Clive but I am familiar with AN2867. Looking at Table 7 I see that there are four 12.5pF crystals recommended for the F7. Okay, I am not using one of them but it should work, and indeed does work if I set high drive strength. The problem is a bug in CubeMx that checks the LSE is operating before setting the drive strength.

In fact I have the 12.5pF MicroCrystal CM7V-T1A on the board but have ordered some 6pF ones to try out.

Mike

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-04-05 08:29 AM

Hi

Forster.Mike

,The issue regarding the reference manual and the CUBEMX code generation has been reported internally for check.

-Nesrine-

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-04 08:11 AM

Hello STM32CubeMX is now fixed.

You can check it out by :

1. Enabling LSE in crystal mode

2. Enabling RTC peripheral

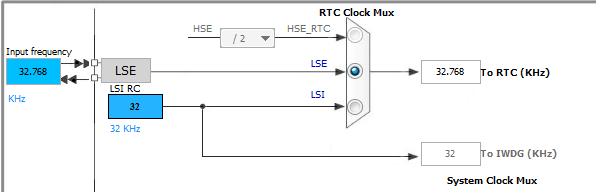

3. On the clock tree select LSE as RTC clock :

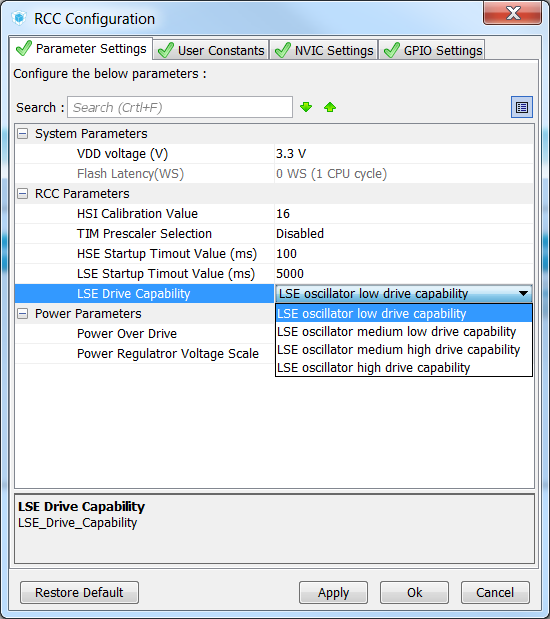

4. Open from the configuration tab, the RCC configuration window and check LSE drive option:

5. generate code and find proper sequence of initialization:

void SystemClock_Config(void)

{ RCC_OscInitTypeDef RCC_OscInitStruct; RCC_ClkInitTypeDef RCC_ClkInitStruct; RCC_PeriphCLKInitTypeDef PeriphClkInitStruct; /**Configure LSE Drive Capability */ __HAL_RCC_LSEDRIVE_CONFIG(RCC_LSEDRIVE_HIGH); /**Configure the main internal regulator output voltage */ __HAL_RCC_PWR_CLK_ENABLE(); __HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE3); /**Initializes the CPU, AHB and APB busses clocks */ RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSI|RCC_OSCILLATORTYPE_LSE; RCC_OscInitStruct.LSEState = RCC_LSE_ON; RCC_OscInitStruct.HSIState = RCC_HSI_ON; RCC_OscInitStruct.HSICalibrationValue = 16; RCC_OscInitStruct.PLL.PLLState = RCC_PLL_NONE; if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK) { _Error_Handler(__FILE__, __LINE__); }- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-04 10:24 AM

Wouldn't this be an ideal case where you plug in crystal characteristics and capacitor values, and have the software perform a 'will it blend' kind of test, and select the appropriate drive settings, etc.?

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-05 09:35 AM

Hello!

Are you sure that the generated code is correct?

In my project the LSEDRV is not set with __HAL_RCC_LSEDRIVE_CONFIG(RCC_LSEDRIVE_HIGH), because

at that point there is no write access to Backup domain.

I have solved this bug by moving __HAL_RCC_LSEDRIVE_CONFIG(RCC_LSEDRIVE_HIGH)

to right after the 'Backup domain Write protection disable' code section in the

HAL_RCC_OscConfig function

.I think this is a bug in

STM32CubeMX which has to be solved.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-01 04:53 AM

kermeci is correct that the so called fix to CubeMX doesn't work. As he says the code generated writes to the RCC_BDCR register while it is in Read only mode.

Mike

- STM32 act as SPI Master and slave for Echo of 1byte Data in STM32 MCUs Embedded software

- Problem with external oscillator : not able to flash anymore in STM32 MCUs Products

- OSC32_IN and OSC32_OUT when are not used for LSE on STM32F070CBT in STM32 MCUs Products

- H7RS HSE Analog Bypass Oscillators in STM32 MCUs Products

- STm32f407: Which Registers control HSI or HSE oscillator selection and PLL clock source? in STM32 MCUs Products