Is it possible to use continuous clock for bank #2 only ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-06-29 11:50 PM

Hello,

We try to configure bank #2 , PSRAM, in synchronous continuous clock, while keeping the other banks (bank #1 - NOR flash, and bank #3 - sram memory) as asynchronous.

On trying to do the change directly in code, it didn't work.

We than noticed that cubeMX also gives a "warning" message in the FMC configuration window as following:

NOR/PSRAM common continuous clock

ContinuousClock3

Diagnostic:

To be able to enable the continuous clock generation, first switch to the Pinout view and set to burst read (or burst read write) the Clock mode of the memory for which the Chip Select mode is set to NE1.

Parameter Description:

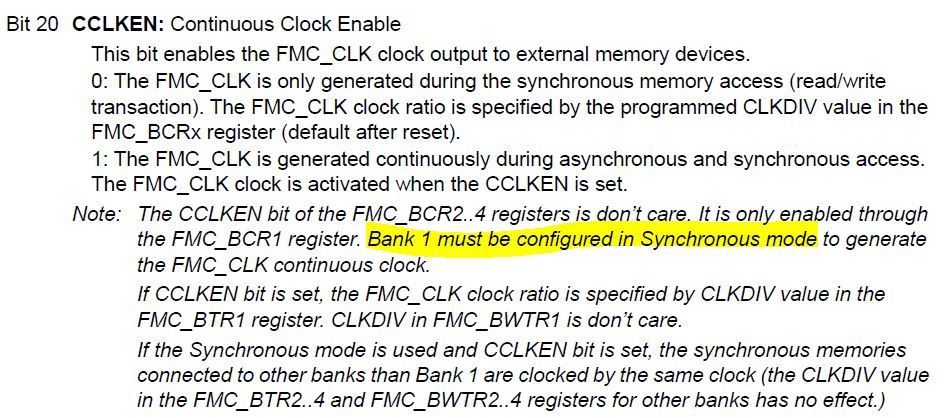

There is only one continuous clock enable bit located in sub-bank Bank 1 - NOR/PSRAM 1.

We than check the device reference (stm32h743), it also says that BANK #1 should be configured as synchronous clock.

So, the question is:

Is it sufficient to configure bank #1 clock as continuous clock, or is it also required to configure it as synchronous ?

If the 2nd option is the correct (bank #1 must be set as synchronous), does it mean that we can't keep using bank #1 as asynchronous, only because we need bank #2 to have continuous clock ?

Thanks,

ranran

Thanks,

ranran

- Labels:

-

FMC-FSMC

-

STM32H7 series