- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: How to use BDMA in STM32H7?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to use BDMA in STM32H7?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-12-08 01:53 AM

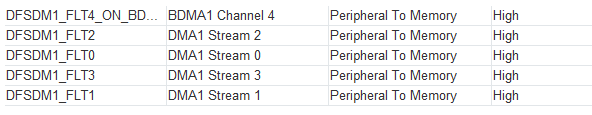

I am trying to read signals from digital MEMS microphones via DFSDM peripheral and transfer it to memory with DMA on STM32H7A3. I found out that 4 channels are handled by DMA and remaining 4 with BDMA. Now I can't figure out how to get this BDMA to work.

Below I placed screenshots of Cube configuration and initialization of DFSDM with DMA. I suspect that the problem can be with memory configuration in linker script, since DMA and BDMA has not access to the same memory sections. Do someone have idea if my assumptions are correct and can suggest what should I do to get it to work?

Solved! Go to Solution.

- Labels:

-

DFSDM

-

DMA

-

STM32H7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-16 07:40 AM

Hi Ons,

Unfortunately, we've found out that BDMA doesn't have parallel channels. So even if it would start working it wouldn't suit our needs. Thank You very much for your support.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-12-08 05:31 AM

Hi Natan Stec,

Can you please share your .ioc file.

You also can refer to the STM32CubeH7 Firmware where you can find DFSDM examples.

Best Regards,

Ons.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-12-08 05:43 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-12-08 05:58 AM

Unfortunately in those examples only 2 channels are being used which are working with DMA. Whereas I have a problem with DFSDM channels 5-8 which uses BDMA.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-12-09 04:14 AM

Hi Natan,

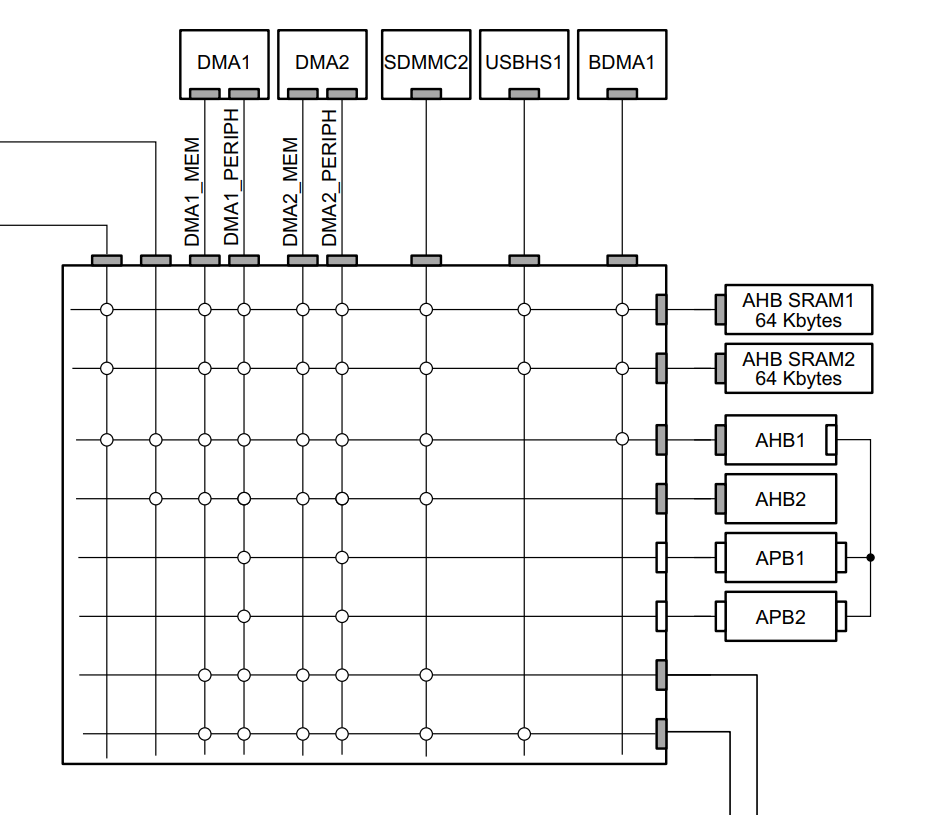

It seems like your RAM starts from 0x2000000 which is the DTCM address , and which is not accessible by DMA or BDMA.

Try to refer to the reference manual and put your code in an accessible memory by DMA or BDMA (AXI SRAM).

Best Regards,

Ons.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-12-22 02:27 AM

Hi,

I've put this struct in memory AHB SRAM1, which is accessible by both DMA and BDMA according to the reference manual. But it, unfortunately, didn't make a difference.

Now I'm wondering if transfer via BDMA requires some different kind of handling. Because now even though I configured it in Circular Mode, BDMA1_IRQHandler fires only once.

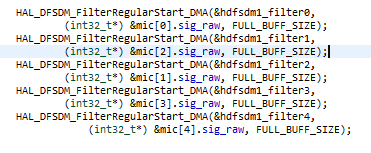

Now I'm starting all channels with the same HAL function (filter 0,1,2,3 uses DMA and filter 4 uses BDMA).

HAL_DFSDM_FilterRegularStart_DMA(&hdfsdm1_filter0,

(int32_t*) &mic[0].sig_raw, FULL_BUFF_SIZE);

HAL_DFSDM_FilterRegularStart_DMA(&hdfsdm1_filter1,

(int32_t*) &mic[1].sig_raw, FULL_BUFF_SIZE);

HAL_DFSDM_FilterRegularStart_DMA(&hdfsdm1_filter2,

(int32_t*) &mic[2].sig_raw, FULL_BUFF_SIZE);

HAL_DFSDM_FilterRegularStart_DMA(&hdfsdm1_filter3,

(int32_t*) &mic[3].sig_raw, FULL_BUFF_SIZE);

HAL_DFSDM_FilterRegularStart_DMA(&hdfsdm1_filter4,

(int32_t*) &mic[4].sig_raw, FULL_BUFF_SIZE);Unfortunately, I wasn't able to find any examples of using BDMA.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-12-23 08:05 AM

Hi Natan,

According to the reference manual, "AHB SRAM1 is accessible by all system masters except BDMA through D2 domain AHB matrix." (p135)

Therefore, I don't think that the use of AHB SRAM1 is a good choice.

Best Regards,

Ons

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-12-28 01:36 AM

Hi Ons,

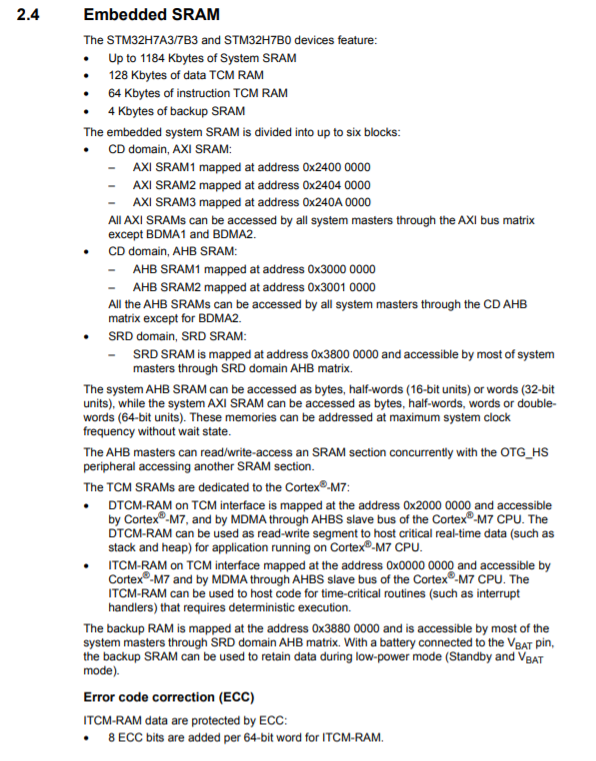

I can't find such info in the reference manual you linked for my MCU - STM32H7A3.

Here is page 135 from this manual.

From this words:

"embedded system SRAM is divided into up to six blocks:

• CD domain, AXI SRAM:

– AXI SRAM1 mapped at address 0x2400 0000

– AXI SRAM2 mapped at address 0x2404 0000

– AXI SRAM3 mapped at address 0x240A 0000

All AXI SRAMs can be accessed by all system masters through the AXI bus matrix except BDMA1 and BDMA2.

• CD domain, AHB SRAM:

– AHB SRAM1 mapped at address 0x3000 0000

– AHB SRAM2 mapped at address 0x3001 0000

All the AHB SRAMs can be accessed by all system masters through the CD AHB matrix except for BDMA2."

I deduced that I should put data in AHB SRAM, as I am using BDMA1.

Statement you just mentioned "AHB SRAM1 is accessible by all system masters except BDMA through D2 domain AHB matrix." I could find in the reference manual for MCU - STM32H750VBT6.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-12-28 07:19 AM

Hi Natan,

Yes you are right, sorry for the conflict.

You can use AHB SRAM for STM32H7A3 devices.

For more details, you can refer to this FAQ, taking in consideration that for STM32H7A3 devices there are only 2 domains ( we can say that D1 and D2 are merged into only one domain, and D3 is maintained as SRD Domain, compared to STM32H743/753/750 devices).

Therefore, there is no problem with your linker file since the memory you chose is accessible by both DMA and BDMA.

From my side, I will try to look after your issue.

Best Regards,

Ons.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-12-28 09:08 AM

Hi Ons,

Any example of DFSDM with BDMA usage would be very helpful. Maybe even just a BDMA usage example would help. Since I can't find any.

I have to get this working on this particular MCU because it is the only one with 8 DFSDM channels.

- SDCard with SDMMC on STM32H755ZI Nucleo in STM32 MCUs Embedded software

- One chip solution for STM32H7 or N6-series? in STM32 MCUs Products

- Functional Safetey U5 Series in STM32 MCUs Products

- Rotate screen 180 degrees in STM32 MCUs TouchGFX and GUI

- Use ST's HAL, or write own libraries? in STM32 MCUs Embedded software