- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Does SPI in slave mode threestate MISO on inactive...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Does SPI in slave mode threestate MISO on inactive NSS, or not?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-17 02:22 PM

This is a followup to

https://community.st.com/thread/40921-multi-slave-spi-using-stm32f7s&sharpcomment-157367

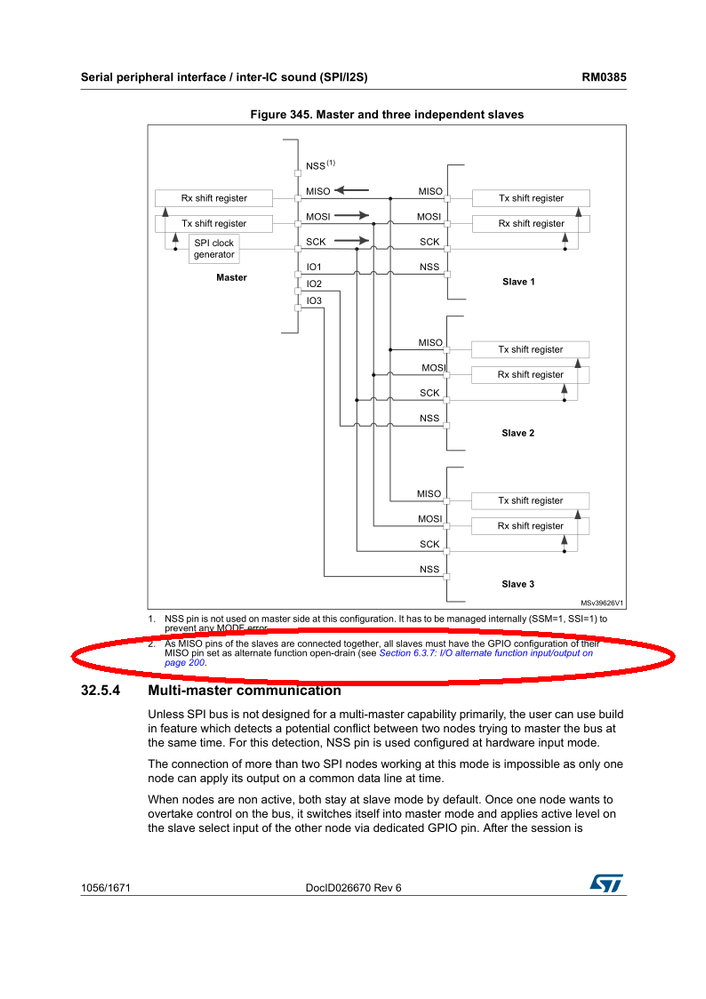

.RM0385, requests MISO being set to open-drain when multiple slaves are connected. This indicates, that NSS set to the inactive state *does not* threestate MISO in STM32 SPI set to slave, as is the custom with SPI. This makes using multiple STM32 SPI slaves not practical.

Other than this, I could not find any indication of MISO behaviour in this regard in the RM.

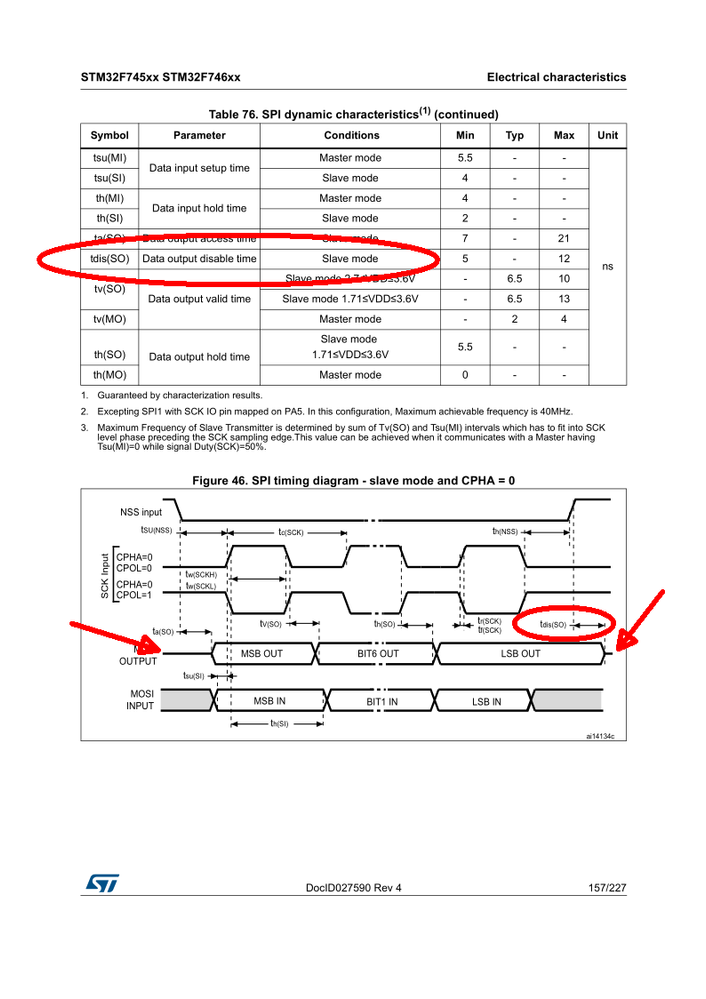

I also went to the respective datasheet and the graph indicates that MISO *does* threestate when NSS goes inactive:

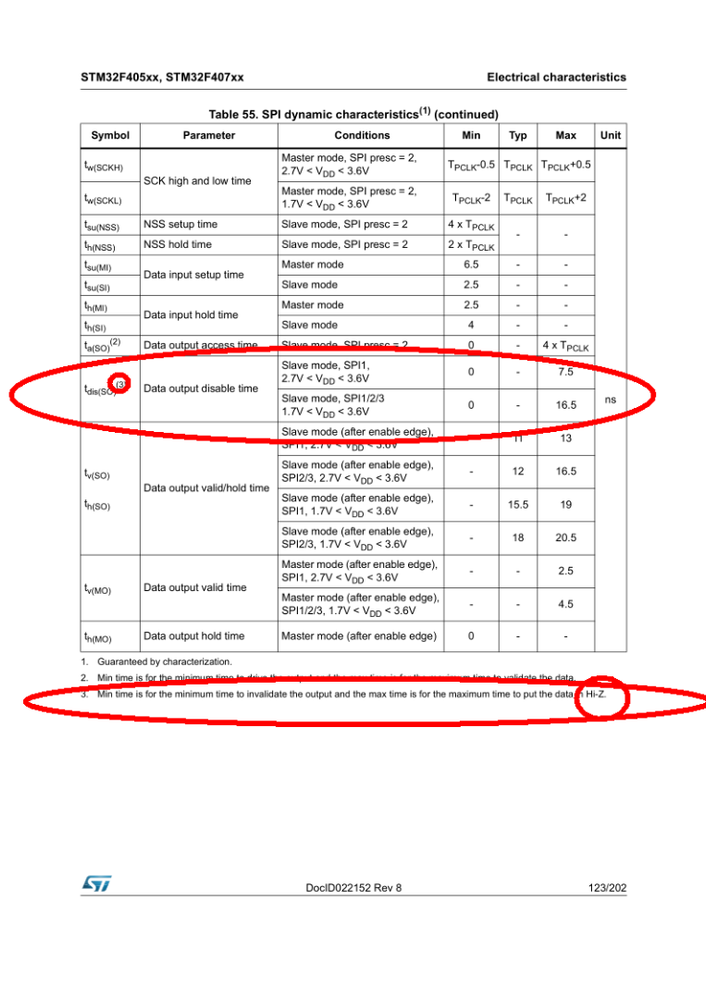

The STM32F40x DS, in the same table, for the same parameter, the footnote clearly states that MISO is to be threestated (put to Hi-Z)

ST, please comment.

Jan Waclawek

nullSolved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-18 04:03 AM

Hello,

MISO signal output is under standard chip select control of NSS input when the SPI slave is enabled and configured at HW NSS mode with NSS output disabled (SPE=1, SSM=0 nad SSOE=0). This allows multi-slave star topology communication.

Best regards,

Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-18 04:03 AM

Hello,

MISO signal output is under standard chip select control of NSS input when the SPI slave is enabled and configured at HW NSS mode with NSS output disabled (SPE=1, SSM=0 nad SSOE=0). This allows multi-slave star topology communication.

Best regards,

Petr

- STM32U5A9 SPI Hardware SS output enable mode not working as intended in STM32 MCUs Products

- G431RBT6 - Interfacing timer and compare output timer have rather fluctuation timings in STM32 MCUs Products

- Delay of interfacing timer is rather inconsistent in STM32 MCUs Products

- Timer 1 Hallsensor interface - No interrupt from external signal. in STM32 MCUs Products

- How to retrigger an externally triggered timer without changing the output channel state in STM32 MCUs Products