- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: DMA issue - transfer error flag TEIF

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

DMA issue - transfer error flag TEIF

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-08-07 09:55 AM

Hi all,

i'm having issue with DMA on STM32F417, i have configuration DMA1_Stream1 is having trigger updates from TIM6_UP (Channel7), i get after start TIM6 error TEIF1 :( my source code was functional with configuration: DMA2_Stream1 Channel7 + TIM8_UP :( please could you review my sources: ? #define ADC_READ_DMA_TIM_UP TIM6 #define ADC_READ_DMA DMA1_Stream1 static __IO uint8_t ADC_Buffer1[20002]; RCC_APB1PeriphClockCmd( RCC_APB1Periph_TIM6, ENABLE); RCC_AHB1PeriphClockCmd( RCC_AHB1Periph_DMA1, ENABLE); TIM_Cmd( ADC_READ_DMA_TIM_UP, DISABLE); DMA_DeInit( ADC_READ_DMA ); DMA_InitTypeDef DMA_InitStructure; DMA_InitStructure.DMA_FIFOMode = DMA_FIFOMode_Disable; DMA_InitStructure.DMA_FIFOThreshold = DMA_FIFOThreshold_Full; DMA_InitStructure.DMA_MemoryBurst = DMA_MemoryBurst_Single; DMA_InitStructure.DMA_PeripheralBurst = DMA_PeripheralBurst_Single; DMA_InitStructure.DMA_Channel = DMA_Channel_7; DMA_InitStructure.DMA_PeripheralBaseAddr = (uint32_t)(&GPIOE->IDR)+0; DMA_InitStructure.DMA_Memory0BaseAddr = (uint32_t)ADC_Buffer1; DMA_InitStructure.DMA_DIR = DMA_DIR_PeripheralToMemory; DMA_InitStructure.DMA_BufferSize = 20000; DMA_InitStructure.DMA_PeripheralInc = DMA_PeripheralInc_Disable; DMA_InitStructure.DMA_MemoryInc = DMA_MemoryInc_Enable; DMA_InitStructure.DMA_PeripheralDataSize = DMA_PeripheralDataSize_Byte; DMA_InitStructure.DMA_MemoryDataSize = DMA_MemoryDataSize_Byte; DMA_InitStructure.DMA_Mode = DMA_Mode_Normal; DMA_InitStructure.DMA_Priority = DMA_Priority_High; // VeryHigh DMA_Init(ADC_READ_DMA, &DMA_InitStructure); TIM_TimeBaseInitTypeDef TIM_TimeBaseStructure; TIM_TimeBaseStructure.TIM_Period=9; TIM_TimeBaseStructure.TIM_Prescaler = 0x0000; TIM_TimeBaseStructure.TIM_ClockDivision = 0; TIM_TimeBaseStructure.TIM_CounterMode = TIM_CounterMode_Up; TIM_TimeBaseInit( ADC_READ_DMA_TIM_UP, &TIM_TimeBaseStructure); TIM_UpdateRequestConfig( ADC_READ_DMA_TIM_UP, TIM_UpdateSource_Regular ); TIM_DMACmd( ADC_READ_DMA_TIM_UP, TIM_DMA_Update, ENABLE); DMA_ITConfig( ADC_READ_DMA, DMA_IT_TC, ENABLE); DMA_Cmd( ADC_READ_DMA, ENABLE); DMA_ClearFlag( ADC_READ_DMA, DMA_FLAG_TCIF1 | DMA_FLAG_TEIF1 ); USARTdebug_puthex_32bit( DMA1->LISR ); TIM_Cmd( ADC_READ_DMA_TIM_UP, ENABLE); Delay(0xaff); USARTdebug_puthex_32bit( DMA1->LISR ); USARTdebug_puthex_32bit( DMA_GetCurrDataCounter(ADC_READ_DMA) ); output is: 00000000 00000200 00004e1f Thanks for all replies, Kind regards,Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-23 10:18 AM

Jive should have a better way of closing out old threads, and provide a means to ask a related/linked question.

Until then posters should pay attention to whether they are waking a zombie thread from 5 years ago when they randomly Google or find it via forum search.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-08-07 10:01 AM

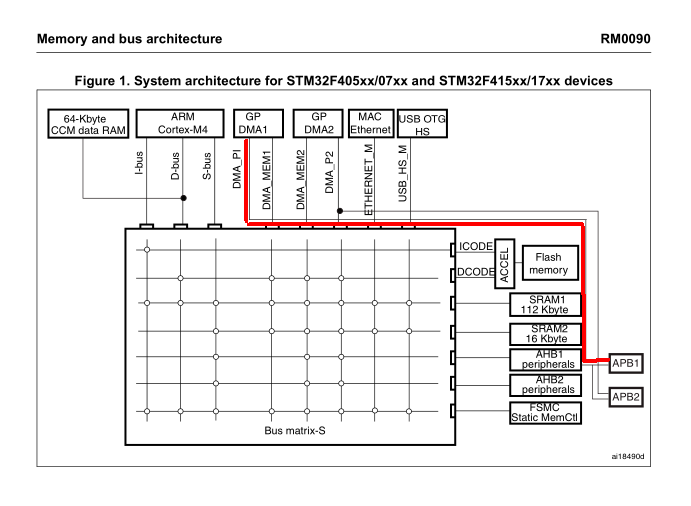

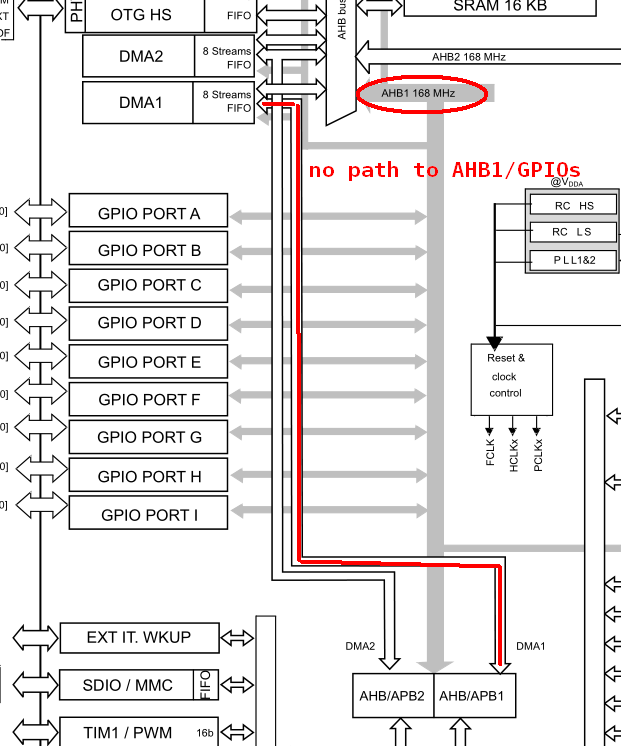

You'll probably want to be using DMA2 to transact with a peripheral on AHB1, which would be classified as a Memory-to-Memory

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-08-07 10:05 AM

well, i need to use DMA1 for transfer GPIOE to memory,

and DMA2 i will use for different purposes, is the DMA1 usable for my purpose ? do i have some mistake in initialization ?- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-08-07 10:27 AM

DMA1 and DMA2 have multiple streams

To rephrase, DMA1 talks between peripherals on APB1 and memory. It won't talk to peripherals on APB2 or AHB1 (GPIOE) AHB1, APB2 and Memory are classified as ''memory'', only DMA2 permits memory-to-memory transfers.Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-08-07 10:38 AM

ohhh, :(

i didn't catch that fact :( well my situation is that i need transferring A/D digital results on GPIOE as fast as possible and with roughly same periodicity, i mean delays between sampling of GPIOE, and i need to use USART6 as debug port and it's on DMA2 :( i'm affraid if i use DMA2_Stream1 for GPIOE -> buffer and DMA2_Stream6 for Buffer -> USART_TX i will get various delays between samples of A/D :( what is your opinion ?- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-08-07 11:06 AM

what is your opinion ?

You're going to get some degree of contention between the CPU, DMA1 and DMA2 against memory. Can you deal with a dozen or so cycles of jitter?Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-08-07 11:39 AM

could you please explain the meaning of your question ?

for me it's most important the delays between sampling of GPIOE, and speeds of other streams is not important, i don't sample GPIOE using CPU because i will not have time to process the data ...- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-19 09:29 AM

This should be in the datasheet and Reference Manual.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-19 09:52 AM

Well, it is.

It's repeated as a footnote at the DMA block schematics in the DMA chapter.

That GPIOs are on AHB1 is in Table1.

Both facts can be seen from the block diagram in the DS, too.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-19 10:16 AM

>>This should be in the datasheet and Reference Manual.

A lot of people miss it, you aren't the first, and won't be the last. The RM is the appropriate location, and it is noted several times.

Up vote any posts that you find helpful, it shows what's working..

- STM32H7S3L8 LL DMA USART TX transfer in STM32 MCUs Products

- TouchGFX build errors in STM32 MCUs TouchGFX and GUI

- Acoustic Echo Cancelling U5 in STM32 MCUs Embedded software

- STM32H747 USB with DMA does not work in STM32 MCUs Embedded software

- Flashing Issue with STM32G431RB in IAR Embedded Workbench 8.22.3 After Patch Installation in STM32 MCUs Products