- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Determining the ADC frequency and # of Sampling Pe...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Determining the ADC frequency and # of Sampling Periods

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-10 07:06 PM

Hi folks!

I'm working with a Netduino, which has an STM32F4, running at 168MHz.

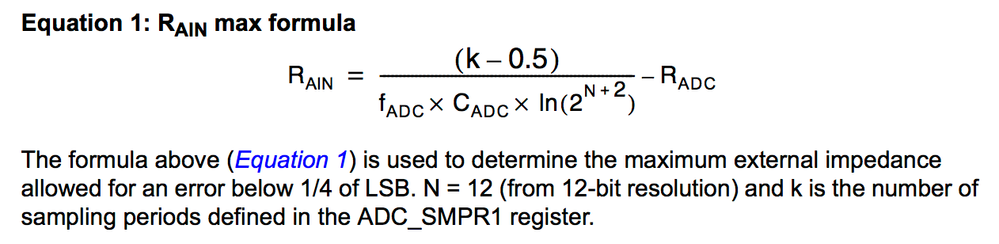

I'm trying to doa calculation (specifically the following), which needs the ADC frequency (

Fadc

) and number of sampling periods (k

:(

I'm having a little trouble tracking these down, however.

Tackling

Fadc

first, , which is peripheral clock / 2 (according to the note next toit). I’m pretty sure from my reading that the peripheral clock is the same as the MCU clock, and my MCU is set to 168MHz. So 168MHz / 2 = 84MHz. However, the data sheet says that the ADC Clock Frequency (fADC) is between 30 and 36MHz for VDDA of 2.5V to 3.6V, and the VDDA on the Netduino should be around 3.3V. So what is the actual value here?For the number of sampling periods, Ifound the following in source:

#

define

STM32_AD_SAMPLE_TIME

2

//

sample time = 28 cyclesADC1->SMPR1 =

0x00249249

*

STM32_AD_SAMPLE_TIME;

So SMPR1 has a hex value of 0x00249249 which is2,396,745 in base 10, so I get 4,793,490 for the number sampling periods, but that can't be right either, considering when I was looking at a sample for the STM32F1, it had a sampling time of 8:

With my answer 6 orders of magnitude off, I think it's probably not right. So I'd appreciate the help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-11 12:16 PM

It's me again.

The ADC group has a programmable prescalar which you set to change the input clock to a value the ADCs can handle. See the ADCPRE field in the Reference Manual ADC_CCR register description.

The sample time register you are reading contains sample time bit fields for 9 or 10 channels. See the Reference Manual definition for the ADC_SMPR1 and ADC_SMPR2 registers.

Hal

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-13 09:05 AM

Ok, that gets me a little further:

0x00249249 * 2 = 0x492492 = b010010010010010010010010

So each of those ADC channels are being set to

010

, or 28 cycles. So if I'm understanding correctly whatk

is, then:k = 28

.But I'm still stuck on

Fadc,

i

t's set to default (0

) in the firmware source, whichis peripheral clock / 2 (according to the note next to it). I’m pretty sure from my reading that the peripheral clock is the same as the MCU clock, and my MCU is set to 168MHz. So 168MHz / 2 = 84MHz. However, the data sheet says that the ADC Clock Frequency (fADC) is between 30 and 36MHz for VDDA of 2.5V to 3.6V, and the VDDA on the Netduino should be around 3.3V. So what is the actual value here?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-13 09:17 AM

ohhh.. that's what you meant by the

ADCPRE.

00: PCLK2 divided by 2

01: PCLK2 divided by 4

10: PCLK2 divided by 6

11: PCLK2 divided by 8

I just need to go find that.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-13 09:31 AM

So I'm back to the beginning on that because:

ADC->CCR =

0

;

Which means those bits are 00, or PCLK/2, which is 84MHz.

What am I missing here?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-13 11:22 AM

Maybe not you but the original author of that code?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-13 01:36 PM

You seem to be missing that these registers are programmable by you, you don't have to accept the reset values. This programming is done in your software prior to enabling and starting the ADC.

Hal

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-13 02:30 PM

Correction - do you have access to the code to determine what the ADCPRE field is set to prior to enabling and starting the ADC ?

Hal

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-13 09:11 PM

,

,

Yes. I linked to it in the original question: ,

,- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-14 07:37 AM

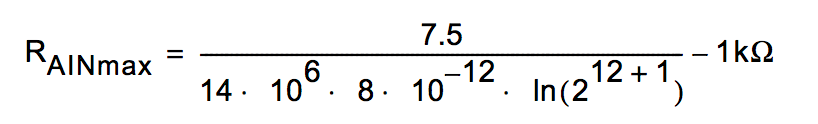

The max allowable ADC frequency as a function of Vdda is as you noted, but the ADC can run slower. For your case, ADCPRE should be set to at least 2 (divide by 6, Fadc = 28 MHz), unless of course there is some other not visible to us clock configuration code or hardware that initializes PCLK to less than 168 MHz.

The sampling time can also be changed by changing the ADC_SMPR1 SMP10 field to as much as 7 to get a sampling time of as much as 480 cycles. Only Channel 10 is being converted, so ADC_SMPR2 and the other fields of ADC_SMPR1 do not need to be changed unless you decide to convert other channels.

I believe you have all the information now to do your resistance calculation.

Hal

- STM32H563 ADC Prescaler in STM32CubeIDE (MCUs)

- OPENAMP STM32H745 memory problems in STM32 MCUs Embedded software

- Differential ADC measurment with Zephyr (STM32H563RG) in STM32 MCUs Embedded software

- How to change VSO0 to VSO1 in RCC? in STM32 MCUs Boards and hardware tools

- BLE Connection Interval in STM32 MCUs Wireless