- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- About Ouput Compare Insert dead time .

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

About Ouput Compare Insert dead time .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-06 12:30 AM

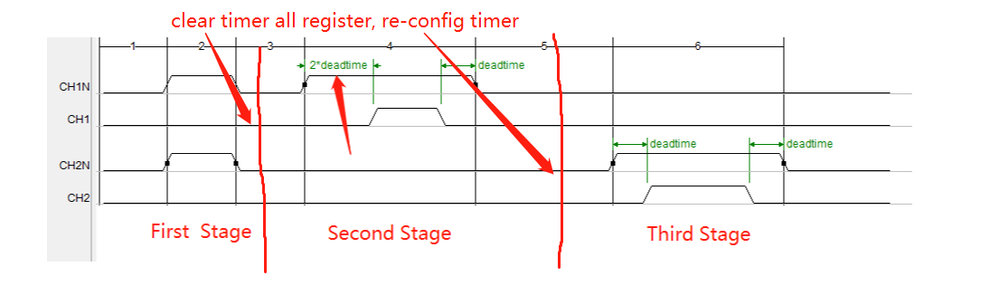

Now , I generate below waveform. Every thing is OK except for red arrow , it indicate a deadtime.but it's longer than other deadtime , in fact , This dead time is twice as large as the other dead time .

divide into three stage :

1�?First Stage , TIM register content

CCMR1.OC2M = 1 ;

CCMR1.OC1M = 1;

CCER.CC1NE = 1;

CCER.CC2NE = 1;

CCER.CC1NP = 1;

CCER.CC2NP = 1;

BDTR.OSSR = 1;

BDTR.MOE = 1;

2�?Second Stage

CCMR1.OC1M = 2;

CCER.CC1E = 1;

CCER.CC1NE = 1;

CCER.CC1NP = 1;

BDTR.OSSR = 1;

BDTR.MOE = 1;

3�?Third Stage

CCMR1.OC2M = 2;

CCER.CC2E = 1;

CCER.CC2NE = 1;

CCER.CC2NP = 1;

BDTR.OSSR = 1;

BDTR.MOE = 1;

when every stage completed , clear all resgister, then ,re-config TIM , re-start .

so. I don't know why the second stage dead time have problem .

Solved! Go to Solution.

- Labels:

-

TIM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-06 5:44 PM

config CCER before BDTR can be solved

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-06 12:43 AM

This again as in your previous post, may be an artefact from the way how you set up things. Hard to tell without seeing the actual code, and also I don't have time to analyze this thoroughly.

Try to single-step through the code clearing/setting the timer registers (while having the timer stopped, maybe through the DBGMCU freeze registers) and observe the impact of each register change on the outputs.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-06 5:22 AM

yes , I have solved !

thanks for your help all the time .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-06 5:44 PM

config CCER before BDTR can be solved

- Object initialization silently skipped with picolibc due to missing linker symbols in STM32CubeIDE for Visual Studio Code (MCUs)

- Nucleo L452RE SPI: 10us delay after CS going low before SPI SCK starts in STM32 MCUs Embedded software

- QSPI Memory Read Write verification in STM32 MCUs Products

- After firmware flash, first time STOP 3 mode power consumption is higher (if board is not power cycled) in STM32 MCUs Products

- How to test motor current ADC working properly? in STM32 MCUs Motor control