- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- 3 Phase pwm dutycycle with DMA issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

3 Phase pwm dutycycle with DMA issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-17 2:18 AM

Hello,

i am working on a school project regarding 3 phase motor control. I have a nucleo32 board with a stm32f410 device

The ideea is to generate a lookup table for the dutycycle values, and transfer them to the CCR1, CCR2 and CCR3 Timer1 registers

Each channel has complementary outputs (1P/1N 2P/2N 3P/3N) and some little deadtime

Right now i am facing some dificulties when configuring the DMA to update these registers corectly, so i started from a ST timer example, and ending my code in this manner.

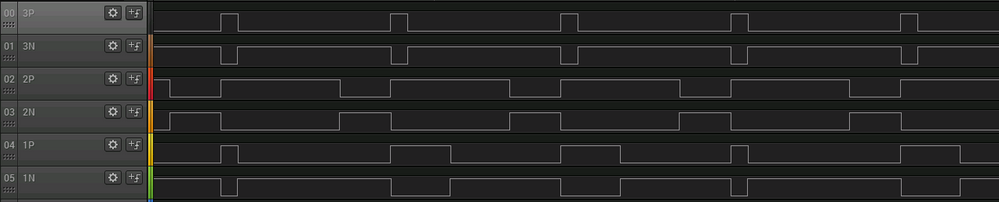

The desired output on each channel should be 10, 35, 70% dutycycle, but its not....

Right now i have random values on the 3 channels.

I am incrementing incorectly the CCRx registers adresses? What could be the issue

#define TIM1_CCR1_ADDRESS 0x40010034 //duty cycle register address of channel 1

uint16_t aSRC_Buffer[3] = {0, 0, 0}; // defined a 3 values buffer

/* PWM MOTOR OUTPUTSPA8 - Channel 1P

PA7 - Channel 1NPA9 - Channel 2PPB0 - Channel 2NPA10 - Channel 3PPB1 - Channel 3N*/

void main() {

GPIO_InitTypeDef GPIO_InitStructure;

DMA_InitTypeDef DMA_InitStructure; /* GPIOA and GPIOB clock enable */ RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOA | RCC_AHB1Periph_GPIOB, ENABLE);/* GPIOA Configuration: Channel 1,2,3 as alternate function push-pull */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_10 | GPIO_Pin_8 |GPIO_Pin_9|GPIO_Pin_7; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF; GPIO_InitStructure.GPIO_Speed = GPIO_Speed_100MHz; GPIO_InitStructure.GPIO_OType = GPIO_OType_PP; GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_UP ; GPIO_Init(GPIOA, &GPIO_InitStructure); GPIO_PinAFConfig(GPIOA, GPIO_PinSource10, GPIO_AF_TIM1); GPIO_PinAFConfig(GPIOA, GPIO_PinSource9, GPIO_AF_TIM1); GPIO_PinAFConfig(GPIOA, GPIO_PinSource8, GPIO_AF_TIM1); GPIO_PinAFConfig(GPIOA, GPIO_PinSource7, GPIO_AF_TIM1); GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0 | GPIO_Pin_1; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF; GPIO_InitStructure.GPIO_Speed = GPIO_Speed_100MHz; GPIO_InitStructure.GPIO_OType = GPIO_OType_PP; GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_UP ; GPIO_Init(GPIOB, &GPIO_InitStructure); GPIO_PinAFConfig(GPIOB, GPIO_PinSource0, GPIO_AF_TIM1); GPIO_PinAFConfig(GPIOB, GPIO_PinSource1, GPIO_AF_TIM1);/* DMA clock enable */

RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_DMA2 , ENABLE); /* Stream 6 is for duty cycle on TIM1 channel 1,2,3 */ DMA_DeInit(DMA2_Stream6); DMA_InitStructure.DMA_Channel = DMA_Channel_6; DMA_InitStructure.DMA_PeripheralBaseAddr = (uint32_t)(TIM1_CCR1_ADDRESS) ; DMA_InitStructure.DMA_Memory0BaseAddr = (uint32_t)aSRC_Buffer; DMA_InitStructure.DMA_DIR = DMA_DIR_MemoryToPeripheral; DMA_InitStructure.DMA_BufferSize = 3; DMA_InitStructure.DMA_PeripheralInc = DMA_PeripheralInc_Enable; DMA_InitStructure.DMA_MemoryInc = DMA_MemoryInc_Enable; DMA_InitStructure.DMA_PeripheralDataSize = DMA_PeripheralDataSize_HalfWord; DMA_InitStructure.DMA_MemoryDataSize = DMA_PeripheralDataSize_HalfWord; DMA_InitStructure.DMA_Mode = DMA_Mode_Circular; DMA_InitStructure.DMA_Priority = DMA_Priority_High; DMA_InitStructure.DMA_FIFOMode = DMA_FIFOMode_Disable; DMA_InitStructure.DMA_FIFOThreshold = DMA_FIFOThreshold_Full; DMA_InitStructure.DMA_MemoryBurst = DMA_MemoryBurst_Single; DMA_InitStructure.DMA_PeripheralBurst = DMA_PeripheralBurst_Single; DMA_Init(DMA2_Stream6, &DMA_InitStructure);uhTimerPeriod = (SystemCoreClock / 17570 ) - 1;

aSRC_Buffer[0] = (uint16_t) (((uint32_t) 10 * (uhTimerPeriod - 1)) / 100); // 10% duty cycleaSRC_Buffer[1] = (uint16_t) (((uint32_t) 35 * (uhTimerPeriod - 1)) / 100); // 35% duty cycleaSRC_Buffer[2] = (uint16_t) (((uint32_t) 70 * (uhTimerPeriod - 1)) / 100); // 70% duty cycleRCC_APB2PeriphClockCmd(RCC_APB2Periph_TIM1, ENABLE);

/* Time Base configuration */

TIM_TimeBaseStructure.TIM_Prescaler = 0; TIM_TimeBaseStructure.TIM_CounterMode = TIM_CounterMode_Up; TIM_TimeBaseStructure.TIM_Period = uhTimerPeriod; TIM_TimeBaseStructure.TIM_ClockDivision = 0; TIM_TimeBaseStructure.TIM_RepetitionCounter = 0; // how many times the pulse repeatsTIM_TimeBaseInit(TIM1, &TIM_TimeBaseStructure);

TIM_OCInitStructure.TIM_OCMode = TIM_OCMode_PWM2; TIM_OCInitStructure.TIM_OutputState = TIM_OutputState_Enable; TIM_OCInitStructure.TIM_OutputNState = TIM_OutputNState_Enable; TIM_OCInitStructure.TIM_Pulse = aSRC_Buffer[0]; TIM_OCInitStructure.TIM_OCPolarity = TIM_OCPolarity_Low; TIM_OCInitStructure.TIM_OCNPolarity = TIM_OCNPolarity_Low; TIM_OCInitStructure.TIM_OCIdleState = TIM_OCIdleState_Set; TIM_OCInitStructure.TIM_OCNIdleState = TIM_OCIdleState_Reset; TIM_OC1Init(TIM1, &TIM_OCInitStructure); TIM_OC2Init(TIM1, &TIM_OCInitStructure); TIM_OC3Init(TIM1, &TIM_OCInitStructure);/* Enable preload feature */

TIM_OC1PreloadConfig(TIM1, TIM_OCPreload_Enable); TIM_OC2PreloadConfig(TIM1, TIM_OCPreload_Enable); TIM_OC3PreloadConfig(TIM1, TIM_OCPreload_Enable); /* Automatic Output enable, Break, dead time and lock configuration*/ TIM_BDTRInitStructure.TIM_OSSRState = TIM_OSSRState_Enable; TIM_BDTRInitStructure.TIM_OSSIState = TIM_OSSIState_Enable; TIM_BDTRInitStructure.TIM_LOCKLevel = TIM_LOCKLevel_1; TIM_BDTRInitStructure.TIM_DeadTime = 11; TIM_BDTRInitStructure.TIM_Break = TIM_Break_Enable; TIM_BDTRInitStructure.TIM_BreakPolarity = TIM_BreakPolarity_High; TIM_BDTRInitStructure.TIM_AutomaticOutput = TIM_AutomaticOutput_Enable;TIM_BDTRConfig(TIM1, &TIM_BDTRInitStructure);

/* TIM1 counter enable */ TIM_Cmd(TIM1, ENABLE); /* DMA enable*/ DMA_Cmd(DMA2_Stream6, ENABLE); /* TIM1 Update DMA Request enable */ TIM_DMACmd(TIM1, TIM_DMA_CC1, ENABLE); TIM_DMACmd(TIM1, TIM_DMA_CC2, ENABLE); TIM_DMACmd(TIM1, TIM_DMA_CC3, ENABLE);/* Main Output Enable */

TIM_CtrlPWMOutputs(TIM1, ENABLE);}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-18 5:52 AM

CCR1, CCR2 and CCR3 are not contiguous 16-bit numbers, but could be treated as an array of 32-bit numbers. All the duties in your image appear to be around 10%, 35% or 70%, on the wrong channels, but not garbage. Not sure why you are triggering DMA on CCRx either. I think you need to read Page 332 of Reference Manual RM0401.

I recently wrote a driver for an WS2812 LED strip. The data interface is curious: it's basically continuously varying PWM, (but with the duty cycle being one of only two values, representing 0s and 1s in the data). I created a lookup table of the all the necessary duty cycles, and used PWM with DMA to copy the next duty cycle on every timer update (TIM1_UP). I haven't tried it, but suspect that the reference I mentioned helps explain how to set this up for three channels.- STM32H503 – ADC trigger shifting from OFF midpoint at duty > 50% in center-aligned complementary PWM in STM32CubeIDE (MCUs)

- Issue changing clock speed via internal PLL in STM32 MCUs Products

- EVSPIN32G4-DUAL + MCSDK 6.3.2: speed oscillations when only one motor is running in STM32 MCUs Motor control

- STM32N657X0H3Q LTDC works with AXI SRAM framebuffer but issue with TouchGFX. in STM32 MCUs TouchGFX and GUI

- I3C Target Mode: Can TX FIFO Be Loaded in RXFNE for Repeated Start Reads? in STM32 MCUs Products