- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Re: STM32F437ZGT6 with KSZ8463MLI

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F437ZGT6 with KSZ8463MLI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-06-20 3:53 AM

Hello everybody.

I am working in a project withhttp://www.st.com/web/catalog/mmc/FM141/SC1169/SS1577/LN1789/PF253733?s_searchtype=partnumber

connected to ahttp://www.micrel.com/index.php/products/lan-solutions/ieee-1588/article/1-ksz8463ml.html

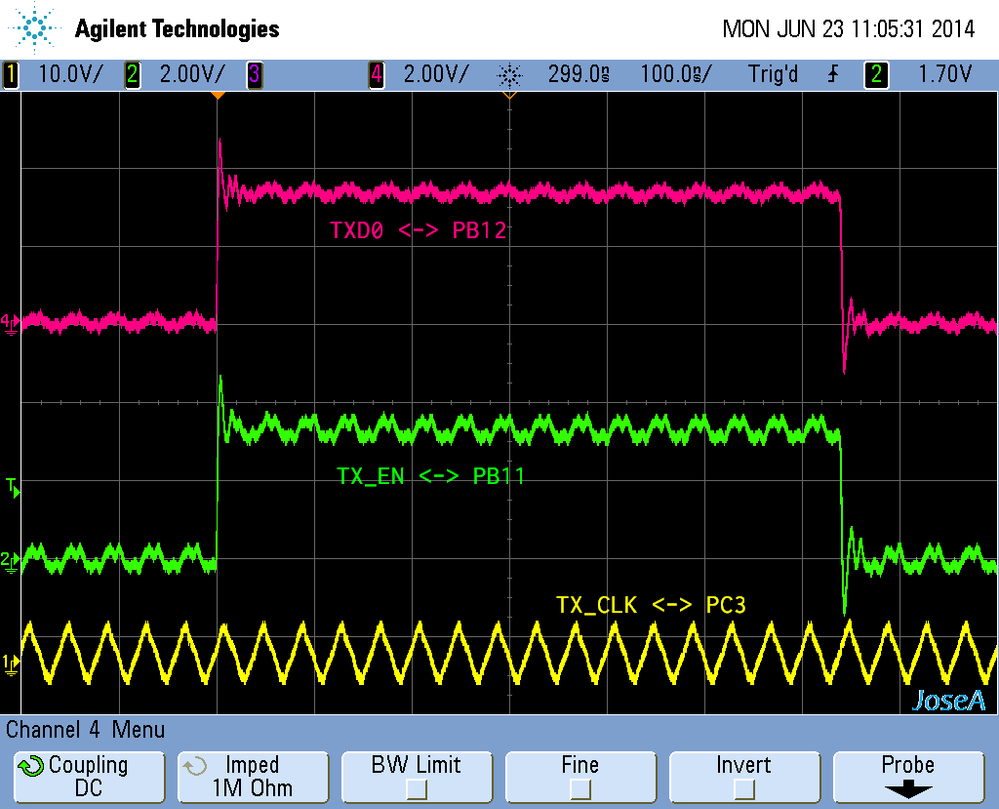

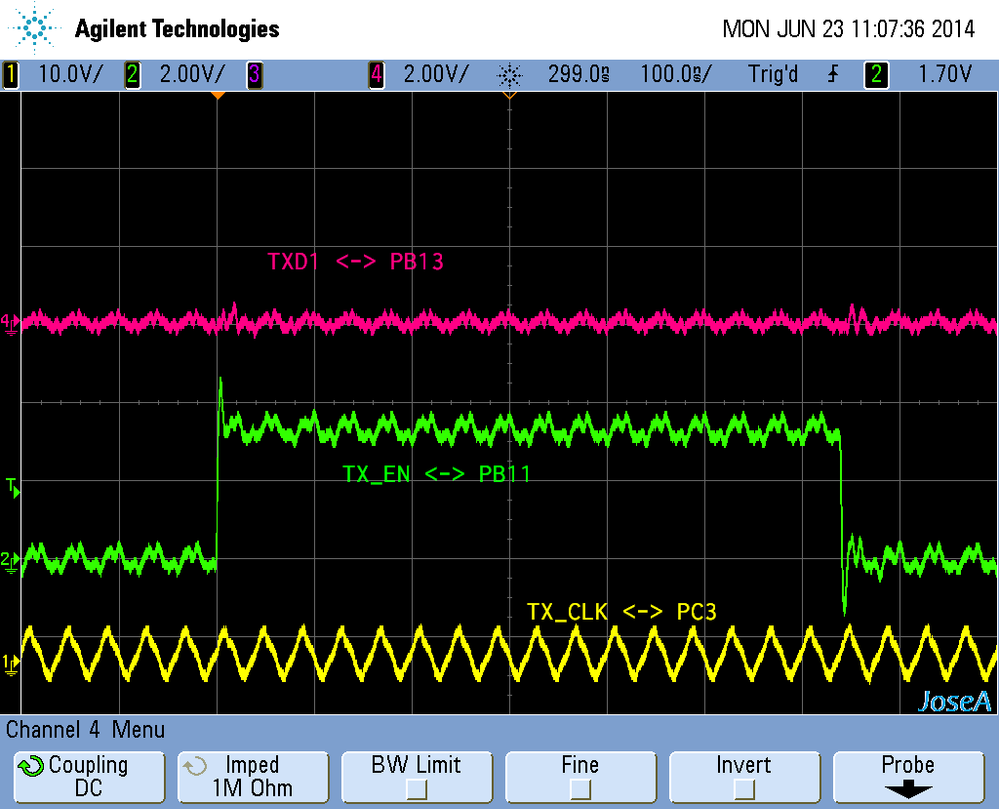

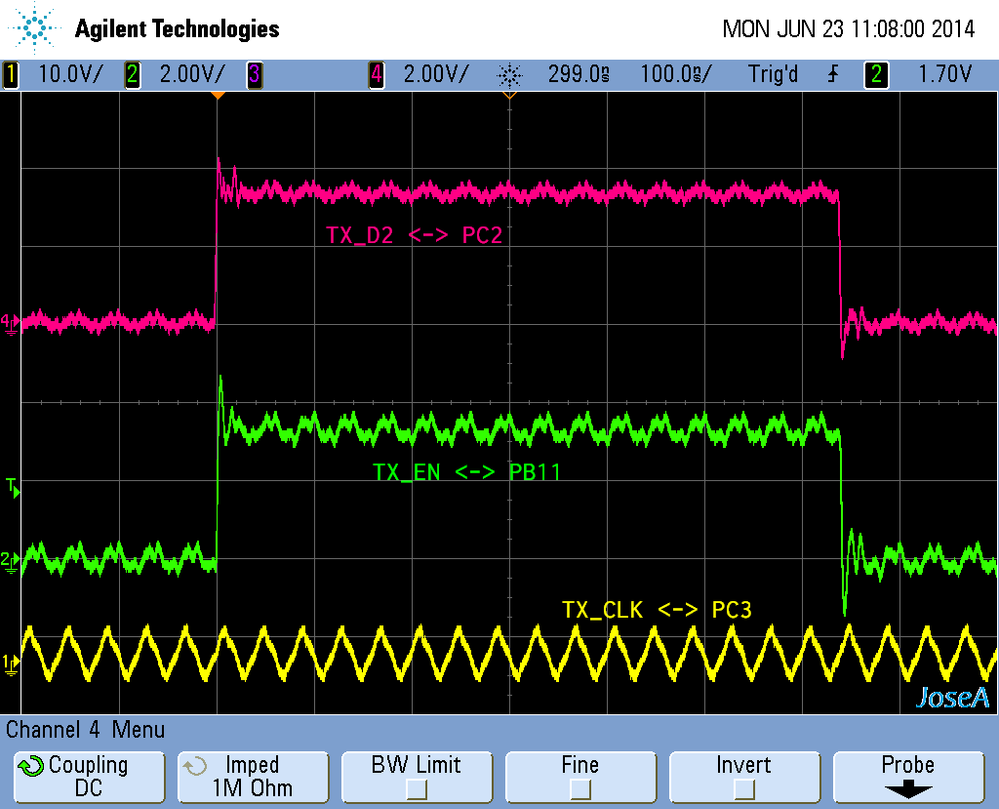

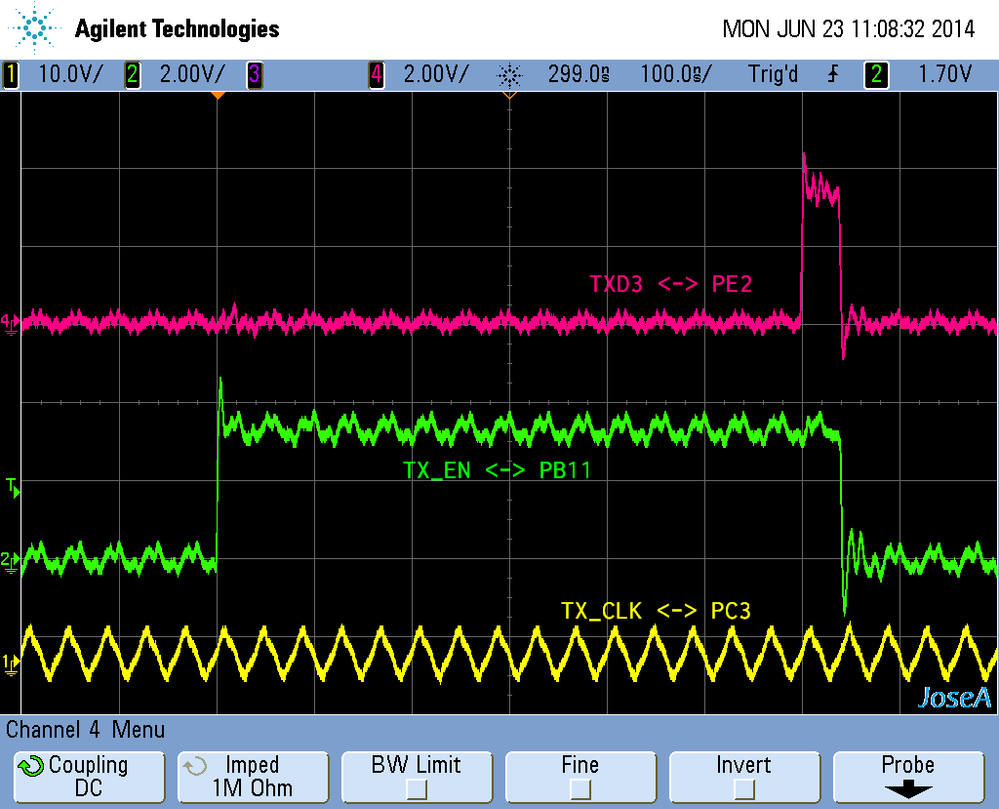

Ethernet transceiver, via MII interface. I am experimenting some trouble with the transmission data pins from STM32F4 (TXD0-3). With an oscilloscope, I have tested this pins and the signal is always the same (and wrong). Reception pins work fine. Also I have tested the same source code with an STM32F4 evaluation board, and all work OK. I wonder if anyone has had similar problems with Ethernet MII connection. Thank you. #mii-ethernet-waveform #stm32f4-micrel-ethernet-mii- Labels:

-

Ethernet

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-06-20 5:03 AM

Issues with Ethernet PHYs usually come down to a couple of things:

Pin configurations and connection. Clock speeds, routing, expectations. PHY configuration address, and internal configuration. I don't see any code or schematics, and don't really know what ''wrong'' means in this context. Suggest you look at other STM32 designs that have used this Micrel part successfully.Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-06-21 3:47 AM

Hello.

At this moment I can't access to the physical device to get the waveforms from the MII interface. I will check these points and I'm trying to upload more information on Monday. Regards, Jose A.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-06-23 2:47 AM

Functions inside stm32f4x7_eth_bsp.c:

void

ETH_BSP_Config(

void

)

{

RCC_ClocksTypeDef RCC_Clocks;

/***************************************************************************

NOTE:

When using Systick to manage the delay in Ethernet driver, the Systick

must be configured before Ethernet initialization and, the interrupt

priority should be the highest one.

*****************************************************************************/

/* Configure Systick clock source as HCLK */

SysTick_CLKSourceConfig(SysTick_CLKSource_HCLK);

/* SystTick configuration: an interrupt every 10ms */

RCC_GetClocksFreq(&RCC_Clocks);

/* Wait until SysTick configuration be successful */

while

(SysTick_Config(RCC_Clocks.HCLK_Frequency / 100) != 0) {

}

/* Set Systick interrupt priority */

NVIC_SetPriority (SysTick_IRQn, 1);

/* Configure the GPIO ports for ethernet pins */

ETH_GPIO_Config();

/* Configure the Ethernet MAC/DMA */

ETH_MACDMA_Config();

/* Init comm with switch */

GPIO_ResetBits(GPIOG, GPIO_Pin_8);

// KSZ8463 Power-down (PWRDN, #17)

GPIO_ResetBits(GPIOG, GPIO_Pin_7);

// KSZ8463 Active reset (RSTN, #63)

Delay(5);

// Wait for switch reset

GPIO_SetBits(GPIOG, GPIO_Pin_8);

// KSZ8463 Normal operation (PWRDN, #17)

GPIO_SetBits(GPIOG, GPIO_Pin_7);

// KSZ8463 Stop reset (RSTN, #63)

Delay(10);

// Wait for switch initialization

printf

(

''CIDER - 0x%

X''

,KSZ_Read(CIDER, 2));

// Check the CIDER register value

if

(EthInitStatus == 0){

LOGERROR(

''Ethernet Init failed, check cable connection

''

);

while

(1);

}

}

static

void

ETH_MACDMA_Config(

void

)

{

ETH_InitTypeDef ETH_InitStructure;

/* Reset ETHERNET on AHB Bus */

ETH_DeInit();

/* Software reset */

ETH_SoftwareReset();

// MUST be BEFORE Ethernet clock enabling !

/* Wait for software reset */

while

(ETH_GetSoftwareResetStatus() == SET);

/* Enable ETHERNET clock */

RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_ETH_MAC | RCC_AHB1Periph_ETH_MAC_Tx |

RCC_AHB1Periph_ETH_MAC_Rx, ENABLE);

/* ETHERNET Configuration --------------------------------------------------*/

/* Call ETH_StructInit if you don't like to configure all ETH_InitStructure parameter */

ETH_StructInit(�?_InitStructure);

/* Fill ETH_InitStructure parametrs */

/*------------------------ MAC -----------------------------------*/

ETH_InitStructure.ETH_AutoNegotiation = ETH_AutoNegotiation_Enable;

// ETH_InitStructure.ETH_AutoNegotiation = ETH_AutoNegotiation_Disable;

// ETH_InitStructure.ETH_Speed = ETH_Speed_10M;

// ETH_InitStructure.ETH_Mode = ETH_Mode_FullDuplex;

ETH_InitStructure.ETH_LoopbackMode = ETH_LoopbackMode_Disable;

ETH_InitStructure.ETH_RetryTransmission = ETH_RetryTransmission_Disable;

ETH_InitStructure.ETH_AutomaticPadCRCStrip = ETH_AutomaticPadCRCStrip_Disable;

ETH_InitStructure.ETH_ReceiveAll = ETH_ReceiveAll_Disable;

ETH_InitStructure.ETH_BroadcastFramesReception = ETH_BroadcastFramesReception_Enable;

ETH_InitStructure.ETH_PromiscuousMode = ETH_PromiscuousMode_Disable;

ETH_InitStructure.ETH_MulticastFramesFilter = ETH_MulticastFramesFilter_Perfect;

ETH_InitStructure.ETH_UnicastFramesFilter = ETH_UnicastFramesFilter_Perfect;

#ifdef CHECKSUM_BY_HARDWARE

ETH_InitStructure.ETH_ChecksumOffload = ETH_ChecksumOffload_Enable;

#endif

/*------------------------ DMA -----------------------------------*/

/* When we use the Checksum offload feature, we need to enable the Store and Forward mode:

the store and forward guarantee that a whole frame is stored in the FIFO, so the MAC can insert/verify the checksum,

if the checksum is OK the DMA can handle the frame otherwise the frame is dropped */

ETH_InitStructure.ETH_DropTCPIPChecksumErrorFrame = ETH_DropTCPIPChecksumErrorFrame_Enable;

ETH_InitStructure.ETH_ReceiveStoreForward = ETH_ReceiveStoreForward_Enable;

ETH_InitStructure.ETH_TransmitStoreForward = ETH_TransmitStoreForward_Enable;

ETH_InitStructure.ETH_ForwardErrorFrames = ETH_ForwardErrorFrames_Disable;

ETH_InitStructure.ETH_ForwardUndersizedGoodFrames = ETH_ForwardUndersizedGoodFrames_Disable;

ETH_InitStructure.ETH_SecondFrameOperate = ETH_SecondFrameOperate_Enable;

ETH_InitStructure.ETH_AddressAlignedBeats = ETH_AddressAlignedBeats_Enable;

ETH_InitStructure.ETH_FixedBurst = ETH_FixedBurst_Enable;

ETH_InitStructure.ETH_RxDMABurstLength = ETH_RxDMABurstLength_32Beat;

ETH_InitStructure.ETH_TxDMABurstLength = ETH_TxDMABurstLength_32Beat;

ETH_InitStructure.ETH_DMAArbitration = ETH_DMAArbitration_RoundRobin_RxTx_2_1;

/* Configure Ethernet */

EthInitStatus = ETH_Init(�?_InitStructure, _PHY_ADDRESS);

}

void

ETH_GPIO_Config(

void

)

{

GPIO_InitTypeDef GPIO_InitStructure;

/* Enable GPIOs clocks */

RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOA | RCC_AHB1Periph_GPIOB |

RCC_AHB1Periph_GPIOC | RCC_AHB1Periph_GPIOI |

RCC_AHB1Periph_GPIOG | RCC_AHB1Periph_GPIOH |

RCC_AHB1Periph_GPIOF, ENABLE);

/* Enable SYSCFG clock */

RCC_APB2PeriphClockCmd(RCC_APB2Periph_SYSCFG, ENABLE);

/* Configure MCO (PA8) */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_8;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_100MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF;

GPIO_InitStructure.GPIO_OType = GPIO_OType_PP;

GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_NOPULL ;

GPIO_Init(GPIOA, &GPIO_InitStructure);

/* MII/RMII Media interface selection --------------------------------------*/

#ifdef MII_MODE /* Mode MII with STM324xG-EVAL */

#ifdef PHY_CLOCK_MCO

GPIO_Init(GPIOA, &GPIO_InitStructure);

/* Output HSE clock (25MHz) on MCO pin (PA8) to clock the PHY */

RCC_MCO1Config(RCC_MCO1Source_HSE, RCC_MCO1Div_1);

#endif /* PHY_CLOCK_MCO */

SYSCFG_ETH_MediaInterfaceConfig(SYSCFG_ETH_MediaInterface_MII);

#elif defined RMII_MODE /* Mode RMII with STM324xG-EVAL */

SYSCFG_ETH_MediaInterfaceConfig(SYSCFG_ETH_MediaInterface_RMII);

#endif

/* Ethernet pins configuration ************************************************/

/* STM3240-EVAL DISCOVERY/My device

ETH_MDIO -------------------------> PA2 PA2 Not connected

ETH_MDC --------------------------> PC1 PC1 Not connected

ETH_PPS_OUT ----------------------> PB5 ---

ETH_MII_CRS ----------------------> PH2 PA0/WKU

ETH_MII_COL ----------------------> PH3 PA3

ETH_MII_RX_ER** ------------------> PI10 PB10

ETH_MII_RXD2 ---------------------> PH6 PB0

ETH_MII_RXD3 ---------------------> PH7 PB1

ETH_MII_TX_CLK -------------------> PC3 PC3

ETH_MII_TXD2 ---------------------> PC2 PC2

ETH_MII_TXD3 ---------------------> PB8 PE2

ETH_MII_RX_CLK/ETH_RMII_REF_CLK---> PA1 PA1

ETH_MII_RX_DV/ETH_RMII_CRS_DV ----> PA7 PA7

ETH_MII_RXD0/ETH_RMII_RXD0 -------> PC4 PC4

ETH_MII_RXD1/ETH_RMII_RXD1 -------> PC5 PC5

ETH_MII_TX_EN/ETH_RMII_TX_EN -----> PG11 PB11

ETH_MII_TXD0/ETH_RMII_TXD0 -------> PG13 PB12

ETH_MII_TXD1/ETH_RMII_TXD1 -------> PG14 PB13

** bypass mode control

*/

/* Configure PA0, PA1, PA2, PA3 and PA7 */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0 |GPIO_Pin_1 |

/* GPIO_Pin_2 |*/

GPIO_Pin_3 | GPIO_Pin_7;

GPIO_Init(GPIOA, &GPIO_InitStructure);

GPIO_PinAFConfig(GPIOA, GPIO_PinSource0, GPIO_AF_ETH);

GPIO_PinAFConfig(GPIOA, GPIO_PinSource1, GPIO_AF_ETH);

// GPIO_PinAFConfig(GPIOA, GPIO_PinSource2, GPIO_AF_ETH);

GPIO_PinAFConfig(GPIOA, GPIO_PinSource3, GPIO_AF_ETH);

GPIO_PinAFConfig(GPIOA, GPIO_PinSource7, GPIO_AF_ETH);

/* Configure PB0, PB1, PB10, PB11, PB12 and PB13 */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0 | GPIO_Pin_1 | GPIO_Pin_10 |

GPIO_Pin_11 | GPIO_Pin_12 | GPIO_Pin_13 ;

GPIO_Init(GPIOB, &GPIO_InitStructure);

GPIO_PinAFConfig(GPIOB, GPIO_PinSource0, GPIO_AF_ETH);

GPIO_PinAFConfig(GPIOB, GPIO_PinSource1, GPIO_AF_ETH);

GPIO_PinAFConfig(GPIOB, GPIO_PinSource10, GPIO_AF_ETH);

GPIO_PinAFConfig(GPIOB, GPIO_PinSource11, GPIO_AF_ETH);

GPIO_PinAFConfig(GPIOB, GPIO_PinSource12, GPIO_AF_ETH);

GPIO_PinAFConfig(GPIOB, GPIO_PinSource13, GPIO_AF_ETH);

/* Configure PC1, PC2, PC3, PC4 and PC5 */

GPIO_InitStructure.GPIO_Pin =

/*GPIO_Pin_1 |*/

GPIO_Pin_2 | GPIO_Pin_3 | GPIO_Pin_4 | GPIO_Pin_5;

GPIO_Init(GPIOC, &GPIO_InitStructure);

// GPIO_PinAFConfig(GPIOC, GPIO_PinSource1, GPIO_AF_ETH);

GPIO_PinAFConfig(GPIOC, GPIO_PinSource2, GPIO_AF_ETH);

GPIO_PinAFConfig(GPIOC, GPIO_PinSource3, GPIO_AF_ETH);

GPIO_PinAFConfig(GPIOC, GPIO_PinSource4, GPIO_AF_ETH);

GPIO_PinAFConfig(GPIOC, GPIO_PinSource5, GPIO_AF_ETH);

/* Configure PE2 */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_2;

GPIO_Init(GPIOE, &GPIO_InitStructure);

GPIO_PinAFConfig(GPIOE, GPIO_PinSource2, GPIO_AF_ETH);

}ETH_GPIO_Config

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-06-23 8:22 AM

Problem

SOLVED

. I will try to explain what was the solution.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2015-09-14 10:21 PM

My STM32F4 shows the exactly same unwanted waveforms on TXD[3:0] in MII Mode. The width of TXEN signal shows also only 600~700 nsec as you have observed. Please share your valuable solution.