- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Re: Issue when using I2C1 and I2C2 simultaneously ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Issue when using I2C1 and I2C2 simultaneously with STM32Cube_FW_F0_V1.9.0.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-11-20 04:37 AM

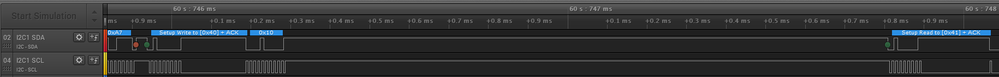

I have been using a stm32f051 as a slave on i2c1 without any problem. Then I started to use it as a master on i2c2 at the same time. This caused the communication on i2c1 to fail with varying frequency. I have been using the i2c drivers with interrupt from the HAL library. I connected a logic analyzer to the i2c lines and located where the error occurred. The first image shows how the part where the error occurs should look like, where the master wants to read from a specific address (0x10) from the slave (the stm32) using a repeated start.

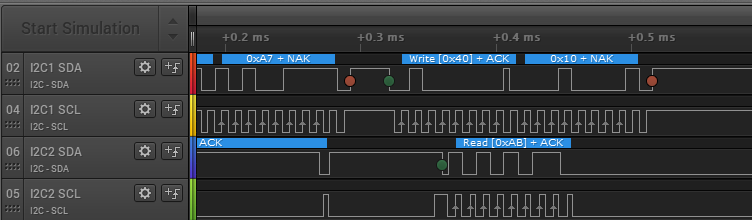

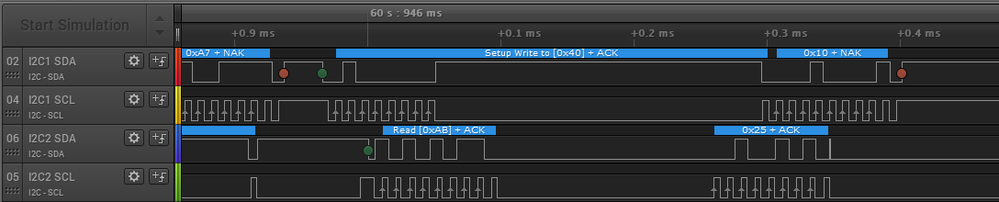

The last two images shows the same part of the communication on i2c1, only here is also communication on i2c2 (stm32 as master).

For some reason the stm32 sends a NACK on i2c1. The error only occurs when the communication on i2c1 and i2c2 are aligned in a specific way, as can be seen in the above images, where there is a write on i2c1 at the same time as a read starts on i2c2.

I couldn't find anything regarding this limitation in the reference manual. So I'm wondering if there is a known error with the i2c hardware that prevents this, or if there is something in the HAL drivers, or if I'm missing something else. All answers are appreciated.

- Labels:

-

I2C

-

STM32Cube MCU Packages

-

STM32F0 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-13 05:33 AM

I have absolutely the same problem with STM32F103C8. Did you fix your problem ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-04-10 11:35 PM

I have the same problem with NUCLEO L4R5ZI board. In my case clk signal goes low and stays there. Any suggestions.

- Can Nucleo-F446 handle 2 CAN channels simultaneously? in STM32 MCUs Boards and hardware tools

- Issue with Multiple ADCs and DMA Configuration on STM32G474RET6 in STM32CubeIDE (MCUs)

- BootLoader and Programming Hardware requirements for custom STM32H753 board in STM32 MCUs Products

- STM32U5 ADC4: possible to enable DMA and AWD at the same time? in STM32 MCUs Products

- STM32 TSC Multi group + multi pin detection problem in STM32 MCUs Products