- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Re: Always getting SPI OVR Error instead of execut...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Always getting SPI OVR Error instead of executing SPI RX callback functions while interfacing SPI1 + DMA + STM32H7

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-06 10:50 AM

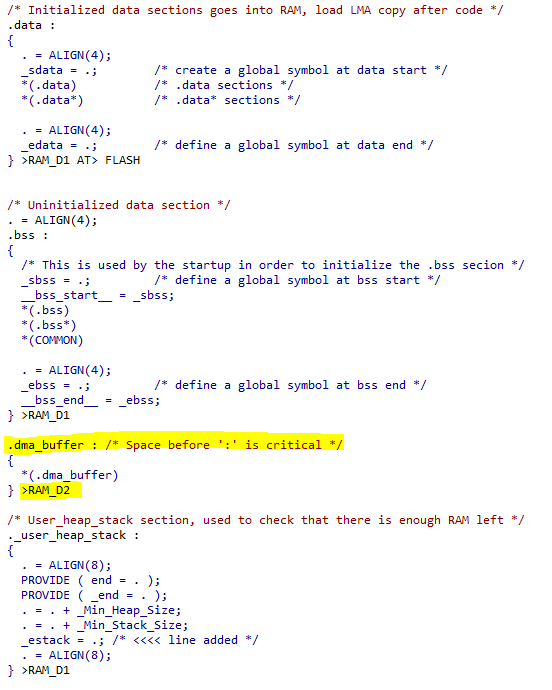

For DMA, allocating the buffer to the right memory segment,

I am already allocating the buffer in to D2 (0x30000000), which I think should be right, and I haven't enabled the cache yet, for remaining all nonvolatile memory allocated in section D1 (0x240000000).

Figure-1 updated STM32H743ZITx_FLASH.ld

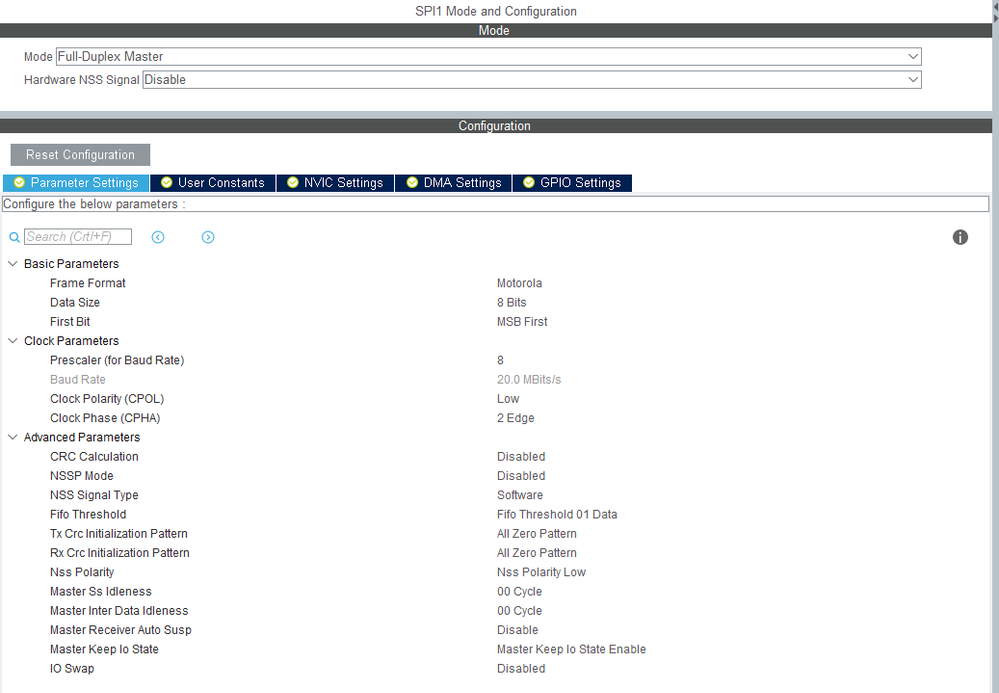

Figure-2 Used SPI configuration in cubeMX:

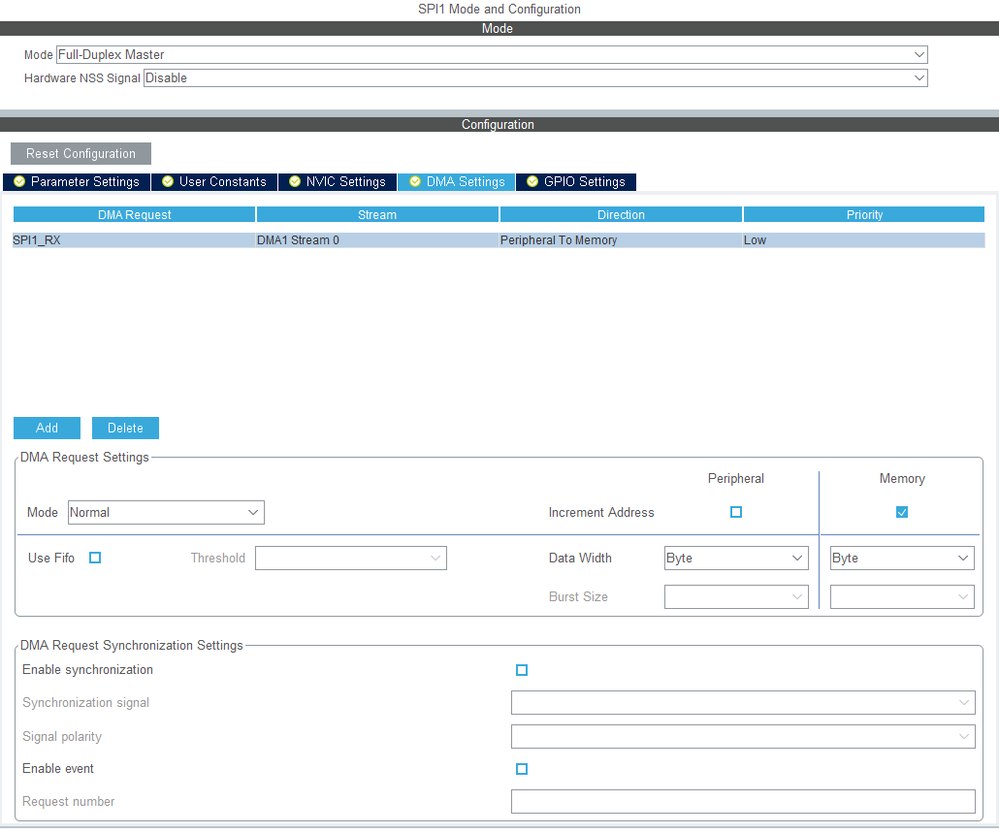

Figure-3: Used DMA configuration in cubeMX:

In program Switching SPI mode in to Receive only master mode,

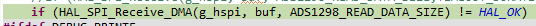

Initiating DMA process by calling function (see Figure-4)

Figure-4

Observed DMA generates interrupts two times, one when half of the buffer is received and another one when the second half is received (whole).

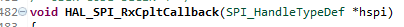

Expecting following function to be called (see Figure-5)

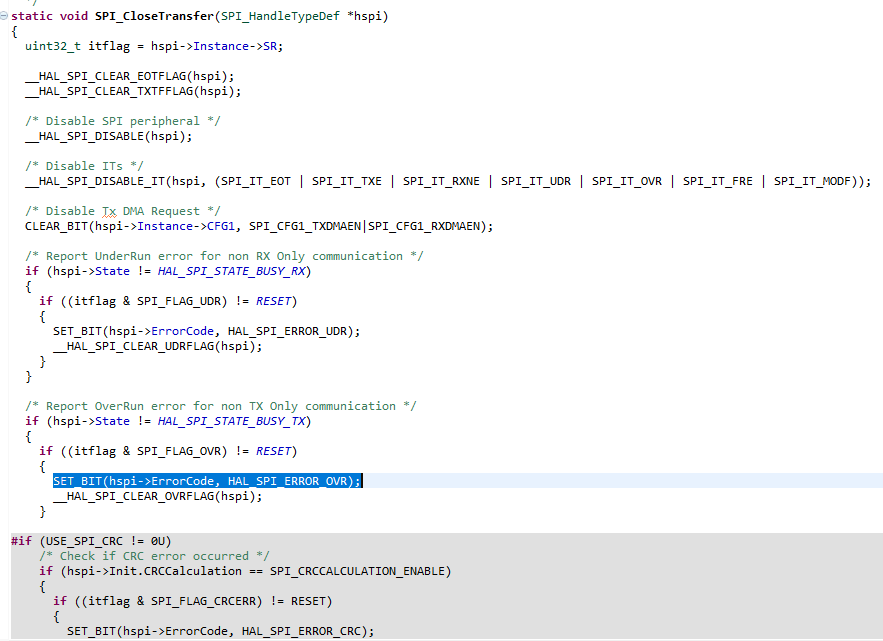

But always getting SPI_ERROR_OVR (see Figure-6)

Figure-6

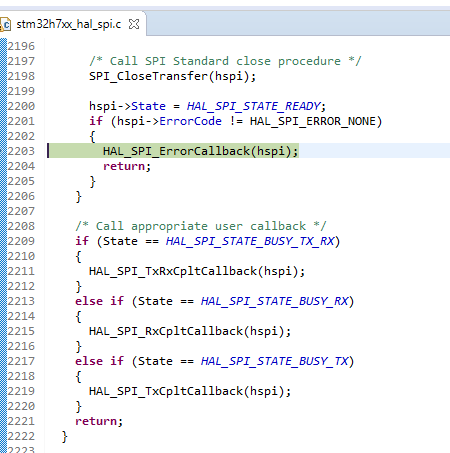

This will eventually calls HAL_SPI_ErrorCallback(hspi) and return instead of HAL_SPI_RxCpltCallback(hspi)

Figure-7

Same experiment works well with STM32F7 but always getting OVER RUN Error in STM32H7.

Means Configuring SPI peripheral to SPI1, using DMA1 and reading data in normal mode, eventually generates the both HT & CT interrupts for DMA, but in CT it always generates the SPI OVER RUN error instead of calling

HAL_SPI_RxCpltCallback(hspi)

How to resolve this issue, Guys please help.

- Labels:

-

DMA

-

SPI

-

STM32Cube MCU Packages

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-13 6:48 AM

Please don't ping me privately about posts on the forum.

I can't help you with CubeMX/HAL defects.

Make sure the buffer is in fact at the address ranges expected. Check what status/errors the DMA unit is reporting.

Check the lengths or transfer units are consistent.

If the DMA is placed in circular mode does it cause errors then? If not points to inconsistent size expectations in transfer.

Check appropriateness of FIFO settings.

Check for off-by-one issues of TX vs RX

Up vote any posts that you find helpful, it shows what's working..

- Adjusting XSPI RAM Clock at runtime in STM32 MCUs Products

- CubeIDE - How can I Debug Step into functions located in ITCM? in STM32CubeIDE (MCUs)

- Font_verdana_20_4bpp_0.cpp: No such file or directory in TouchGFX Designer Tutorial 3 app in STM32 MCUs TouchGFX and GUI

- STM32F429 / STM32G491 What is the difference in external loader? in STM32CubeProgrammer (MCUs)

- SD-card Works in 1-bit mode but it does not work in 4- bit mode. in STM32 MCUs Embedded software